主题中讨论的其他器件: TIDA-01021、 LMK04828、 ADC12DJ3200

您好!

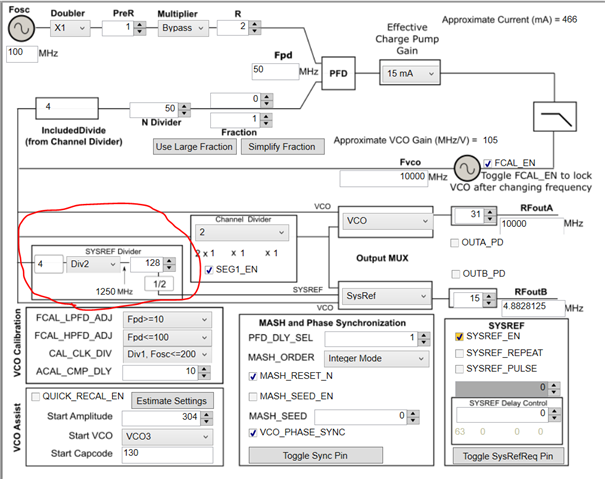

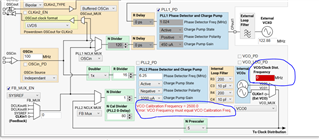

我对 两个需要 实现多芯片同步的 LMX2594的 sysref 时钟是否对齐有疑问。 图1下面列出了我的设置:

- 两个 lmx2594的 OSCIN 由超低偏斜时钟缓冲器提供100MHz 参考时钟

- 两个 lmx2594的 SYSREFREQ 保持高电平、以便在"主器件-连续"模式下工作

- 两个 LMx2594输出10GHz 射频时钟的 RFAout

- 选择两个 lmx2594的 RFBOUT 作为 Sysref 时钟、该时钟为 JESD204B 输出4.8828125MHz 时钟

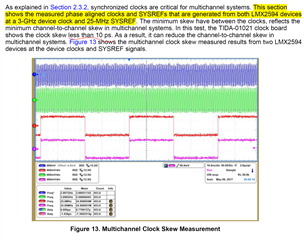

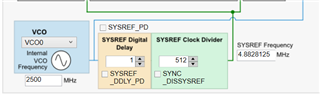

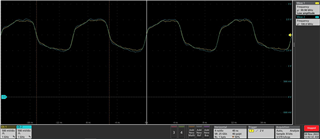

如下图2所示、LMX2594将在类别1下用于 RFAout、这意味着10GHz RFAout 将与100MHz OSCIN 对齐。 图3显示了100MHz OSCIN 在两个 lmx2594之间的对齐情况。 因此、如果 两个 lmx2594的100MHz OSCIN 在引脚位置彼此对齐、则两个 lmx2594的 RFAout 将相互对齐。 但是 、两个 lmk2594的 sysref 时钟不会相互对齐、如图4所示。

当需要实现多芯片同步时、如何在 LMX2594之间对齐 sysref 时钟?

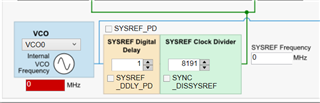

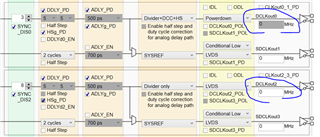

或者、对 JESD_DAC1_CTRL、JESD_DAC2_CTRL、JESD_DAC3_CTRL 和 JESD_DAC4_CTRL 字进行编程以实现对齐、如图5所示?

图1.

图2.

图3.

图4.

图5.

最棒的问候!!!

Jason