你(们)好。

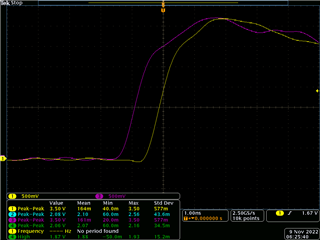

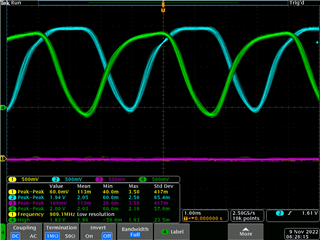

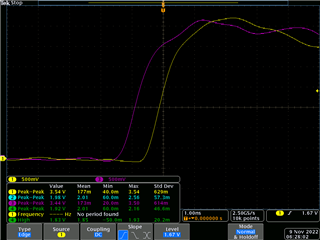

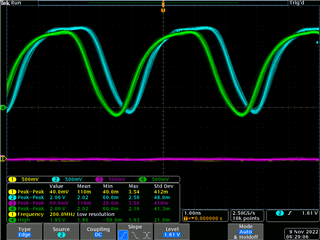

我有两个要同步的 LMK04828。 但是 、在下电上电后、LMKs 的输出器件时钟(DCLKout2)会出现±1 VCO 周期误差。

我没有在 LMK04828上使用任何 PLL。 因此、同步中只涉及分频器复位。

外部1GHz 时钟分配给具有相同路径长度的 LMK1端口。

同步是通过以相同长度同时切换 LMKs 上的 SYNC 引脚来执行的。

对于同步操作、我使用了正常同步模式。 对于 SYSREF 操作、我使用了 SYSREF 脉冲发生器模式。

以下是我的寄存器配置:

(0x0000,0x90) (0x0000,0x10) (0x0000,0x10) (0x0100,0x61) (0x0101,0x22) (0x0103,0x02) (0x0104,0x20) (0x0106,0xf0) (0x0107,0x55) (0x0108,0x64) (0x0109,0x22) (0x010b,0x07) (0x010c,0x20) (0x010e,0x80) (0x010f,0x11) (0x0110,0x61) (0x0111,0x22) (0x0113,0x02) (0x0114,0x20) (0x0116,0xf0) (0x0117,0x57) (0x0118,0x61) (0x0119,0x22) (0x011b,0x02) (0x011c,0x20) (0x011e,0xf0) (0x011f,0x57) (0x0120,0x62) (0x0121,0x22) (0x0123,0x05) (0x0124,0x20) (0x0126,0xb0) (0x0127,0x11) (0x0128,0x68) (0x0129,0x22) (0x012c,0x20) (0x012e,0xf7) (0x012f,0x01) (0x0130,0x61) (0x0133,0x02) (0x0134,0x20) (0x0136,0xf7) (0x0138,0x40) (0x0139,0x00) (0x013a,0x01) (0x013b,0x00) (0x013c,0x00) (0x013d,0x08) (0x013e,0x02) (0x0140,0xf0) (0x0143,0x91) (0x0143,0x91) (0x0143,0x11) (0x0144,0x49) (0x0145,0x7f) (0x0146,0x00) (0x0147,0x10) (0x0148,0x33) (0x0149,0x40) (0x014a,0x02) (0x014b,0x05) (0x014c,0xff) (0x0150,0x00) (0x0156,0x78) (0x015f,0x0b) (0x0161,0x01) (0x0162,0x44) (0x016e,0x13) (0x0171,0xaa) (0x0172,0x02) (0x0173,0x60) (0x017c,0x15) (0x017d,0x33) (0x1ffd,0x00) (0x1ffe,0x00) (0x1fff,0x53) Toggle SYNC pins on LMKs simultaneously (0x0144,0xff) (0x0143,0x12) (0x0139,0x02)

我的问题是、对于 LMK'输出器件时钟对齐、是否预计会发生±1 VCO 周期误差? 我是否错过了同步 LMKs 的任何内容? 我是否应该使用零延迟模式来消除 VCO 周期误差?

谢谢、祝您一切顺利、

Yilun