Other Parts Discussed in Thread: LMK1D1208P, LMK1D1204

主题中讨论的其他器件: LMK1D1204

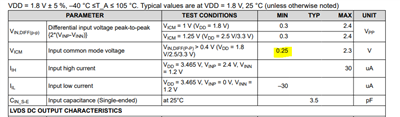

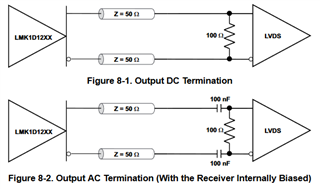

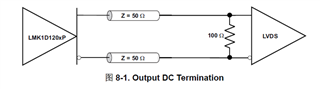

问题1:LMK1D1208P 用作时钟缓冲器。 来自同一芯片的三个100ms 用作三个 FPGA 的系统时钟。 其中两个都可以。 其中一个在调试 DDR3时出现时钟问题。 更换系统时钟后、不会出现问题。 使用直流耦合方法:

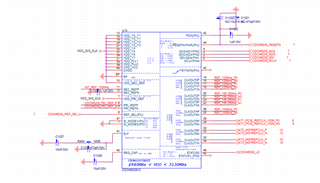

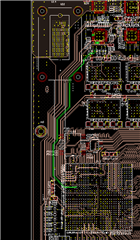

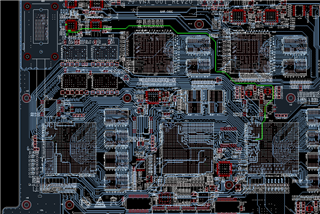

以下是两个 DDR3的 PCB 布线、没有问题:

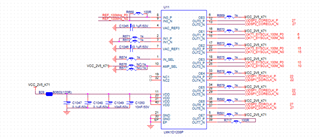

以下是故障 FPGA 的时钟路由:

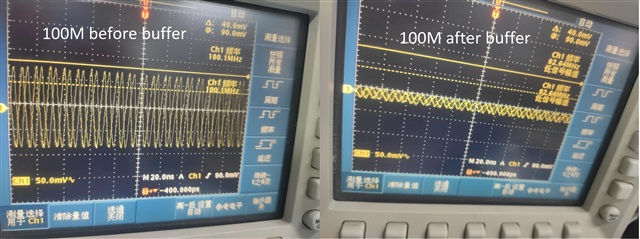

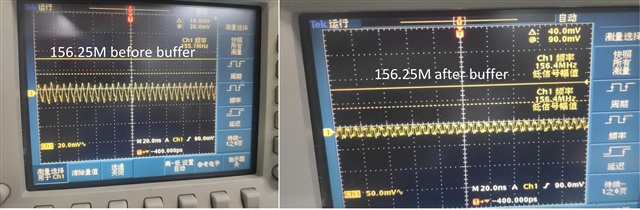

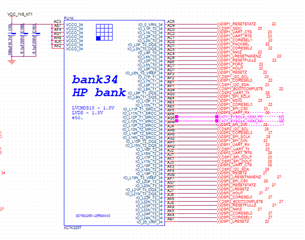

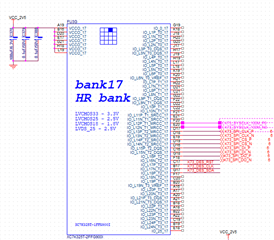

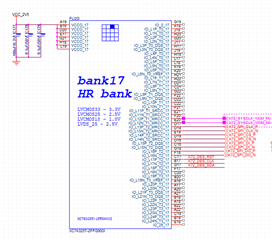

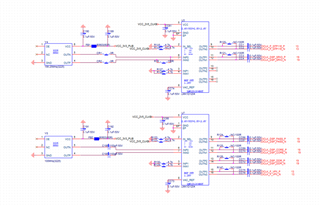

问题2:使用两个 LMK1D1204芯片156.25M 和100M 为 FPGA 的高速端口 BANK116和 BANK115提供时钟。 156.25M BANK116时钟未锁定、100M BANK115用于锁定。 当使用100M BANK116时、它也会锁定、如下所示:

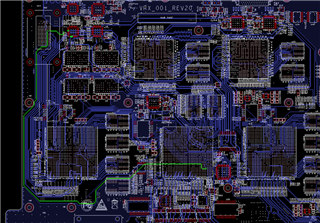

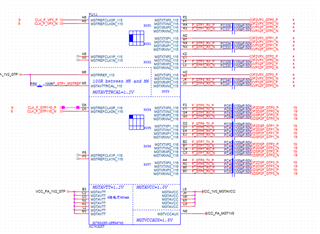

100m PCB 布线的长度为3712.15mil、156.25M PCB 布线的长度为4357.63mil。 PCB 接线图如下: