请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CDCVF2505 你(们)好

在数据表10.2.2详细设计流程中、它显示了

"确定所有时钟输出 Y[3:0]检测到的平均输出负载。"

优化 PLL 传播延迟的第一步。

在下面的情况中、

1Y0=1Y1=4pF、1Y2=1Y3=0pF (未连接)

平均输出负载是 4pF 还是(4pF+4pF+0pF+0pF)/4=2pF?

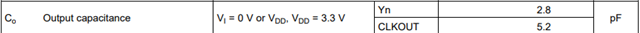

2.对于平均输出负载计算、我们是否应该包括数据表中所示器件的输出电容?

此致、

Ohashi