Dean、

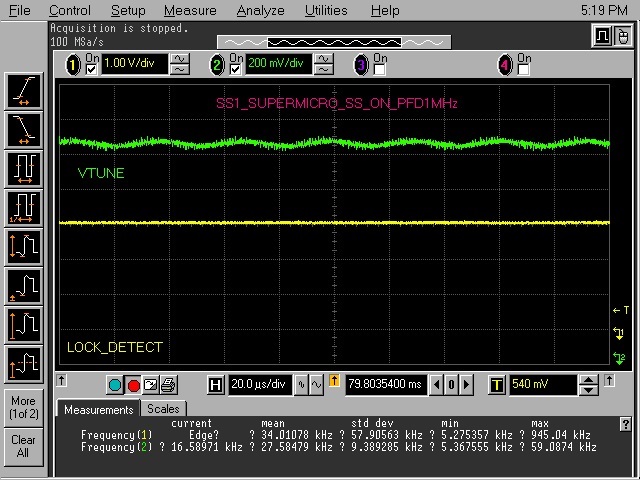

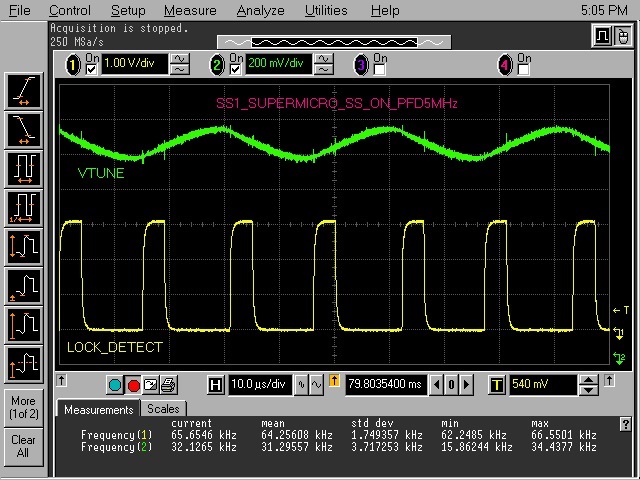

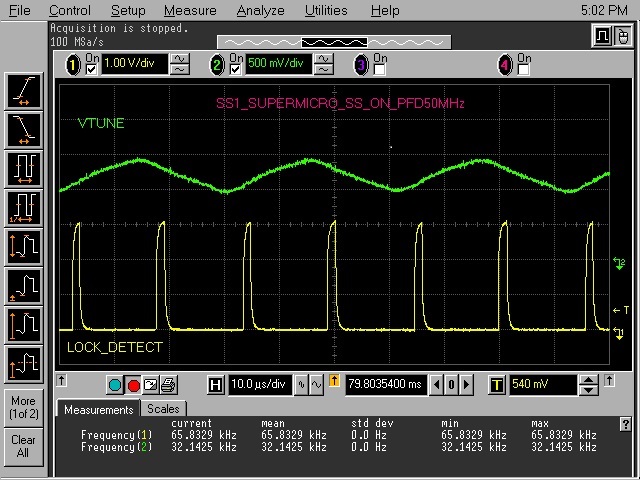

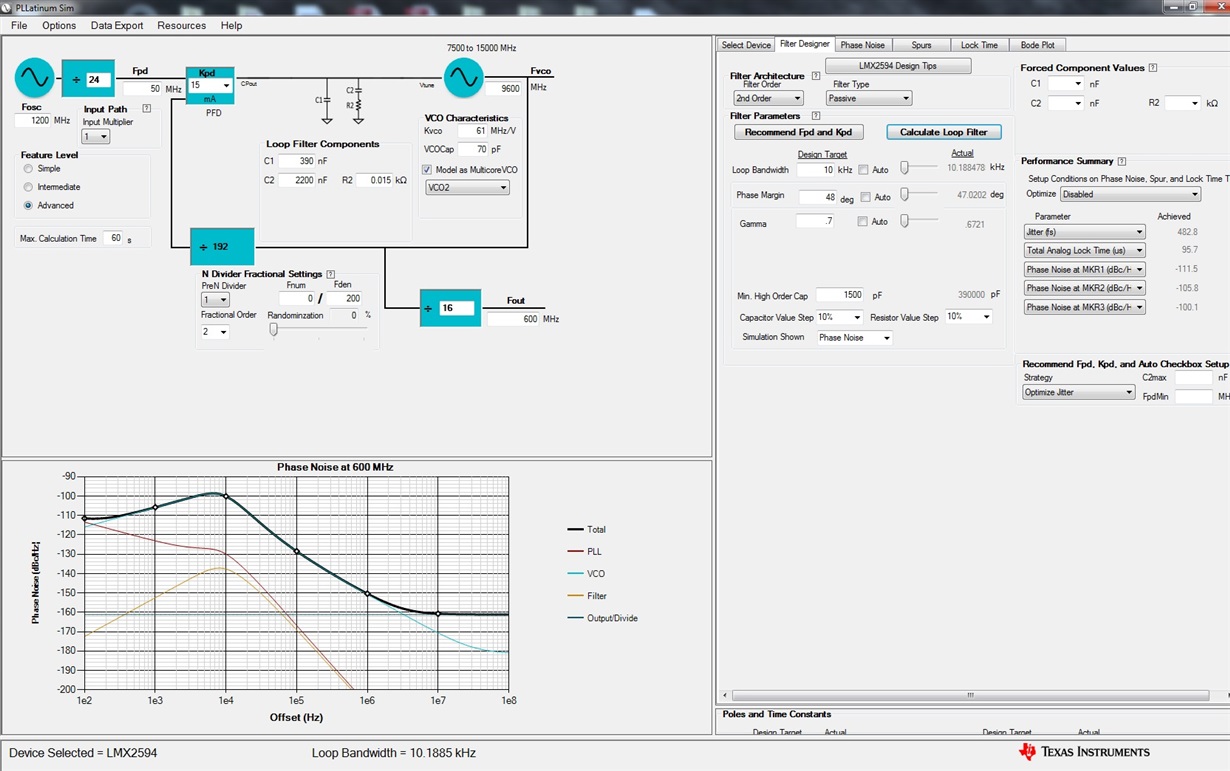

正如我之前在这个论坛上发布的、我们一直在尝试使用 LMX2594来生成一个从1.2GHz 差分时钟源衍生的确定性、边沿锁定的600MHz 输出时钟。 该源是 DDR4 (DIMM)插槽上提供的标准 JEDEC 时钟。 该时钟由扩频调制驱动。 JEDEC 规定在30kHz 调制周期内与基波之间的展频频率偏差为5000PPM。

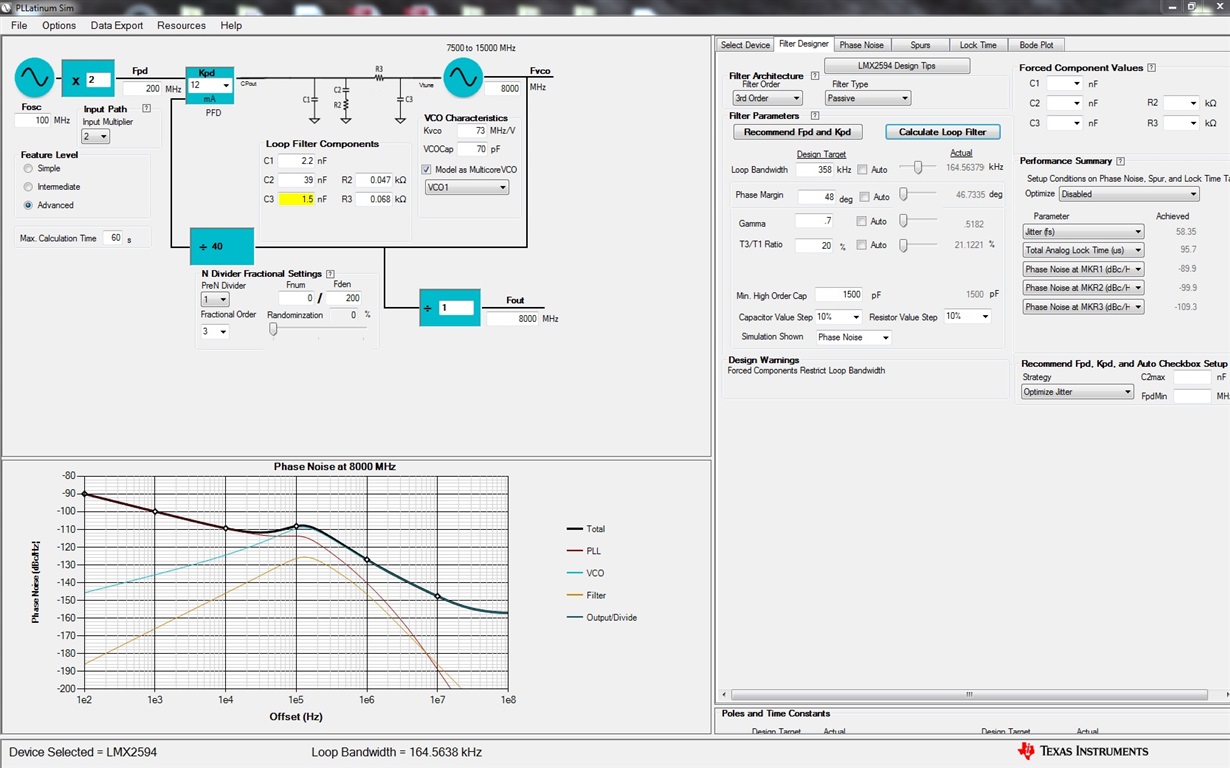

到目前为止、在扩频场景中、我们还无法使用 LMX2594实现确定性锁相。 (但是、当禁用展频时、我们可以实现相位频率锁定)。 由于还有其他 JEDEC 指定的器件和 FPGA 采用可耐展频的 PLL、因此我们期望与 LMX2594一样复杂的器件具有类似的功能。 如果没有、TI 能否确认 LMX2594本身不兼容或不能耐受使用上述扩频调制的 OSC 输入时钟? 或者相反、TI 能否为我们提供有关如何调整 LMX2594和/或支持电路以满足此设计目标的进一步指导?

谢谢、

- Ken