您好!

我的客户对 CDCM6208有疑问。

[问题]

请告诉我如何使用带小数值的 FOD 计算条件下的延迟时间。

[背景]

D/S 中对其进行了如下描述

因此、从 SYNC 引脚置位开始、输出的第一个上升沿大约延迟15ns 至20ns。

我已使用 EVM 确认了这一点。

配置和结果如下。

SYNC_N 引脚中具有函数发生器的输入脉冲(上升时间= 5ns)

SEC 输入= 30.72MHz

VCO = 3072MHz

PS_A = 4

PS_B = 6

Y0 (整数)= 192MHz

Y2 (整数)= 85.333MHz

Y5 (分数)= 76.8MHz (2*5)、77MHz (2*4.987012863)

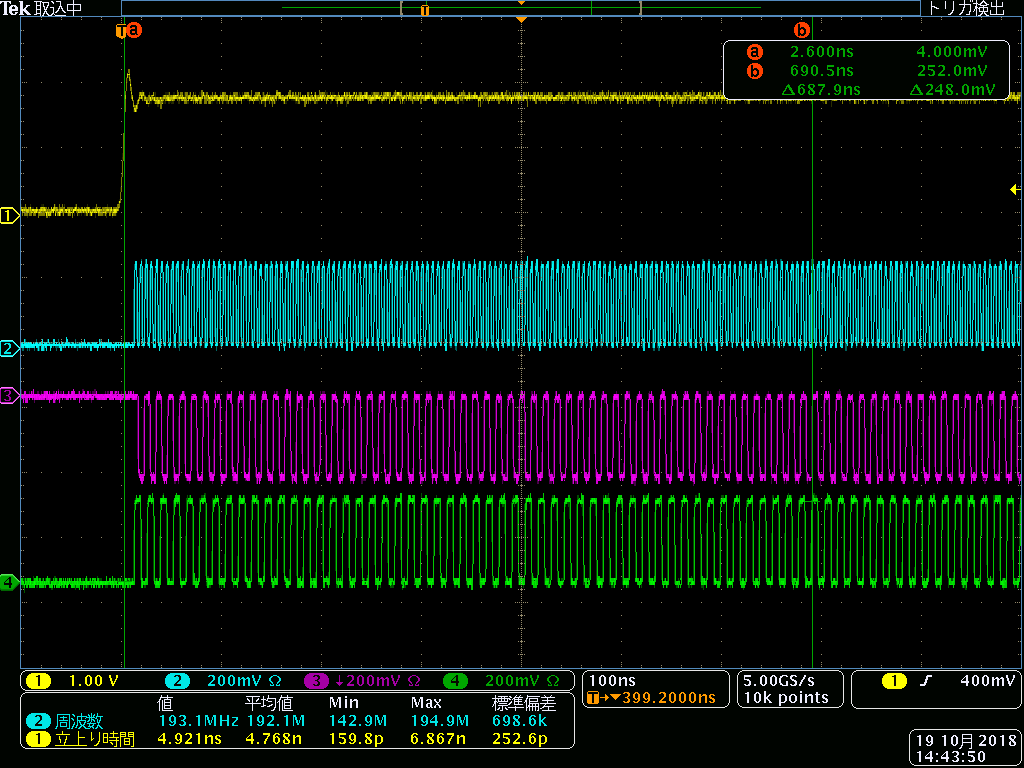

CH1 (黄色)=SYNCN

CH2 (蓝色)=Y0P (以50 Ω 端接 Y0N)

CH3 (紫色)=Y2P (端接 Y2N 、50 Ω)

CH4 (绿色)=Y5P (以 50欧姆端接 Y5N)= 76.8MHz (整数值)

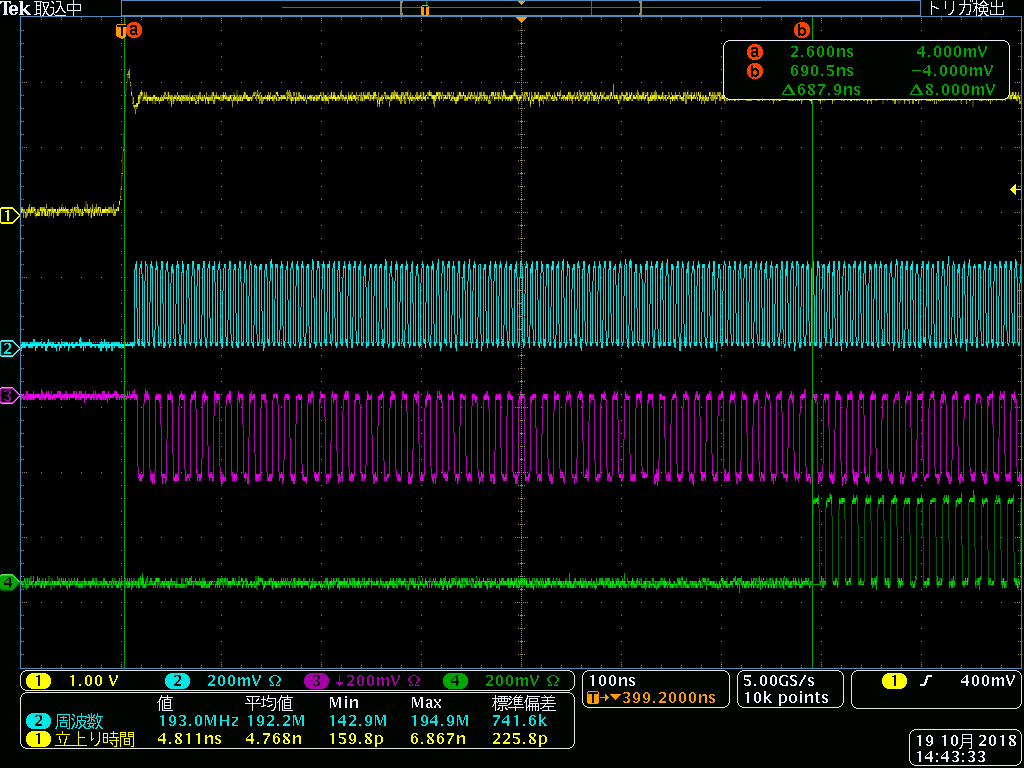

CH1 (黄色)=SYNCN

CH2 (蓝色)=Y0P (以 50 Ω 端接 Y0N)

CH3 (紫色)=Y2P (端接 Y2N 、50 Ω)

Ch4 (绿色)=Y5P (端接 Y5N 、50 Ω) = 77MHz (分数值)

此致、

Hiroshi Katsunaga