您好!

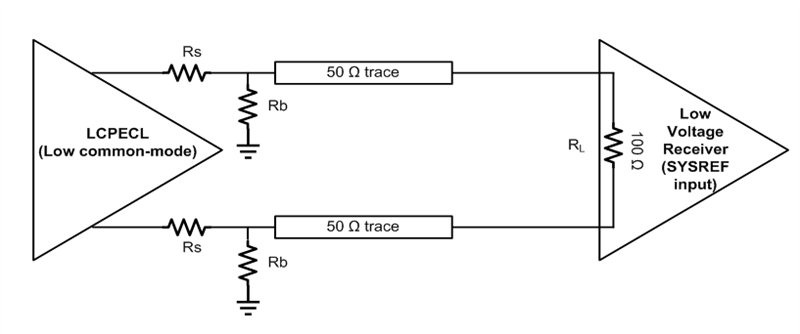

我们希望将 LMK01801时钟缓冲器连接到具有大约1V 输入共模电压(具有集成100 Ω 差分终端的自偏置输入)的直流耦合时钟接收器。 在这种情况下无法应用 LVDS、因为它提供的摆幅不足(最小需要500mVpp 差动摆幅)。 LCPECL 输出格式发挥了作用、这似乎是保持输出到输入共模电压要求的理想选择。 LVPECL 和 LCPECL 的发射极电阻应在120至240欧姆范围内。 但是、我们如何计算最佳电阻器值以在驱动器输出和接收器输入两侧获得大致相同的共模电压?

谁可以在这里提供帮助?

此致、

Joerg