主题中讨论的其他器件:LMX2572、 LMK04828

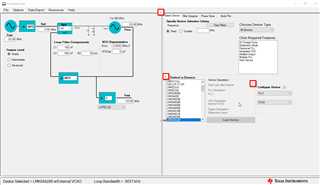

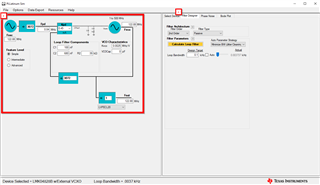

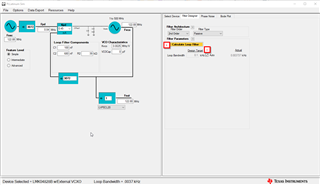

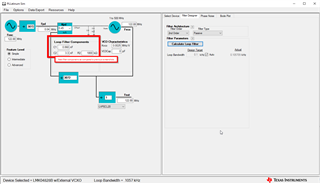

我们正在使用 LMK04828B 板和 TICSpro

我们尝试使用25MHz 输入(CLKin1)生成1GHz 时钟。

在我们的第一个配置中、我们使用 AWG 生成25MHz 的频率、在本例中、CLKin1的抖动非常低、我们可以看到电路板锁定了它(PLL1和 PLL2 LED 均亮起)。 在示波器上进行监控时、我们看到25MHz 和1GHz 相互锁定。

在第二种配置中、我们使用电子板来生成25MHz (CLKin1)。 电路板产生的25MHz 抖动高于 AWG 产生的抖动。 在本例中、我们无法将1GHz 锁定到 CLKin1。 PLL1 LED 熄灭、 但 PLL2 LED 亮起。

作为一项简单的测试、 我们 还使用 PLL+VCO 模型 LMX2572使用抖动25MHz 生成1GHz:此配置工作正常、1GHz 生成的时钟会锁定到抖动25MHz 输入时钟。

我们期望 LMK04828B 的抖动清除器特性能帮助其更好地锁定。 但是、在抖动为25MHz 时、我们无法找到哪些设置组合会使 LMK04828B 生成锁定至25MHz CLKin1的1GHz。 您能解释一下原因并帮助我们进行调试吗?

此致