请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:CDC3RL02 您好!

我使用 CDC3RL02设计了时钟电路、我对 该缓冲器的 MCLK_IN 有疑问。

缓冲器是否接受交流耦合时钟信号作为 MCLK_IN 的输入? (我的设计中进入 MCLK_IN 的输入信号是来自 OCXO 的交流耦合正弦信号)

它在数据表第6页上指定了 MCLK_IN 的技术规格 、如下所示。 我认为这意味着进入 MCLK_IN 的输入信号应该是直流偏置信号。

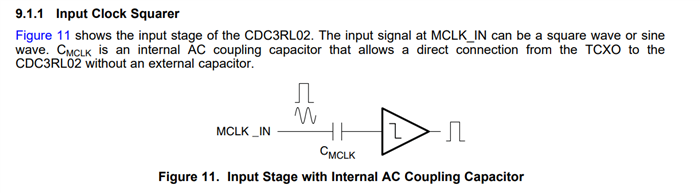

但是、在数据表的第11页、MCLK_IN 输入内部有一个交流耦合电容器、如下所示。 我认为这意味着交流耦合信号也是可以接受的。 所以、我感到困惑。 是否可以将交流耦合正弦时钟应用到 MCLK_IN 中?

感谢您 的建议。

谢谢。