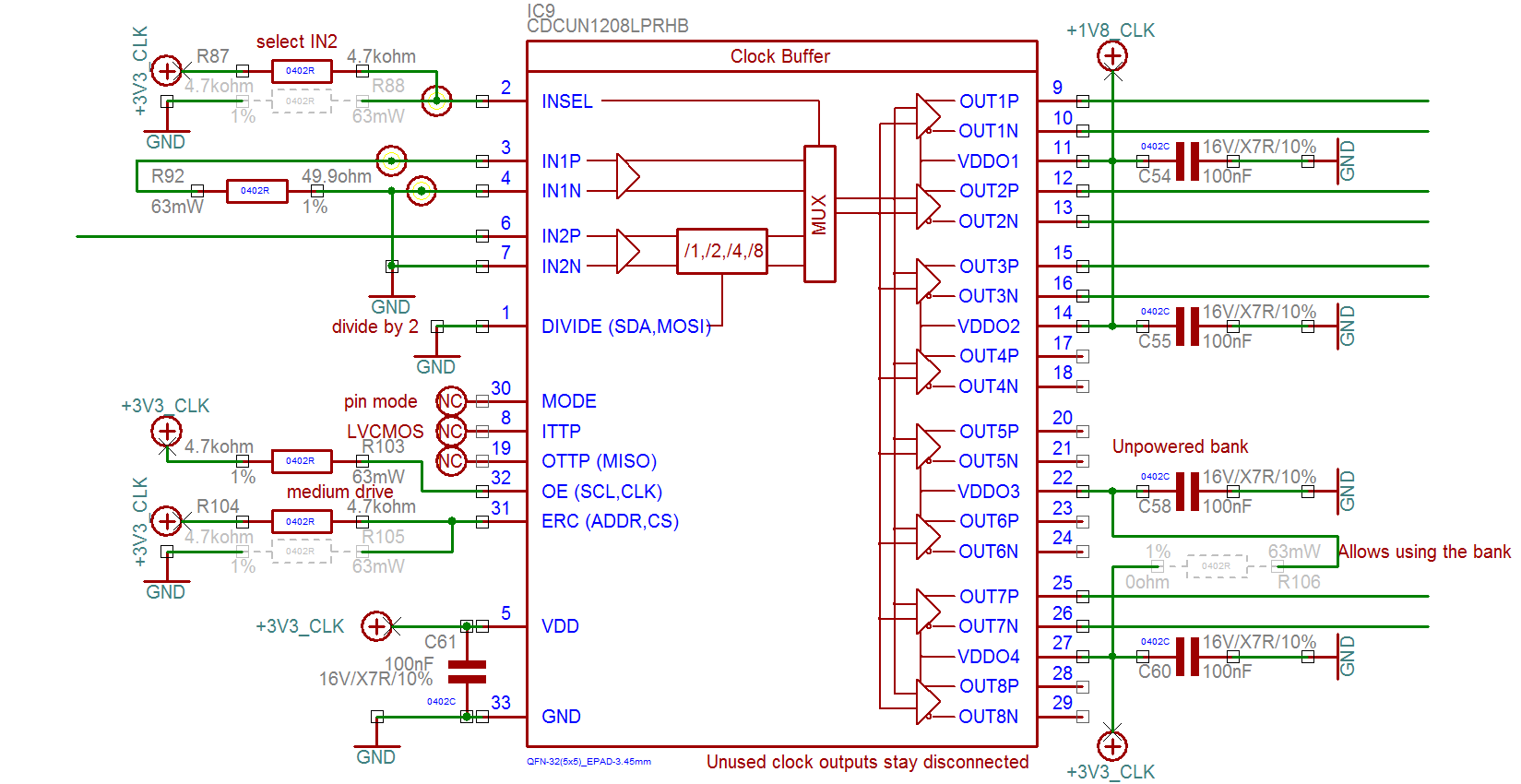

Other Parts Discussed in Thread: CDCUN1208LP

我在尝试加电时遇到 CDCUN1208LP 问题。 配置如下:

- 3.3V 为内核(引脚5)和 VDDO4 (引脚27)供电

- 1.8V 为 VDDO1 (引脚11)和 VDDO2 (引脚14)供电

- VDDO3 (引脚22)悬空、100nF 电容连接到 GND

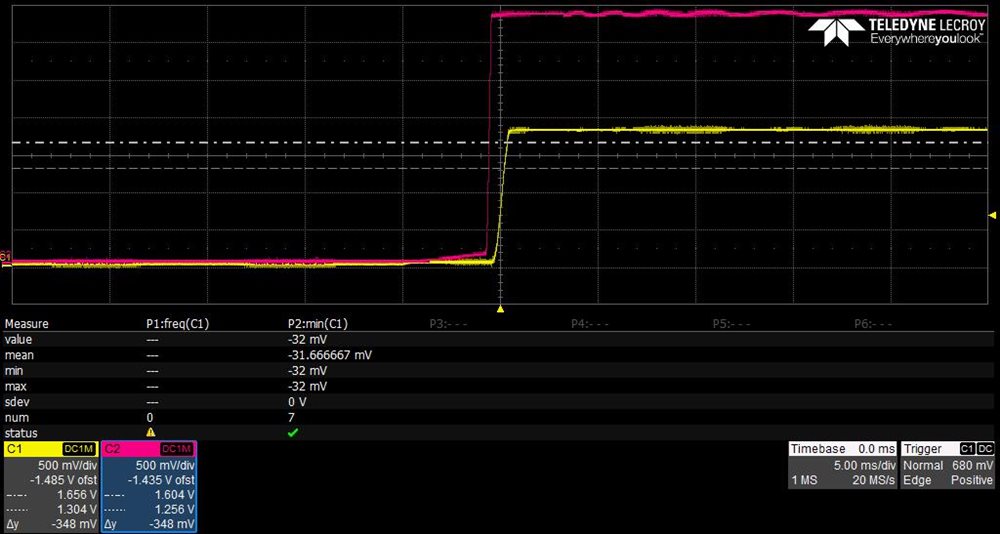

按照以下顺序、CDCUN1208LP 启动并似乎正常工作-在实际开启之前、请注意3.3V 中的电压升高。

我清除了这个凸点(电路板没有其他更改)、并且使用以下(更好的外观)序列、CDCUN1208LP 不再开始!

我认为我尊重芯片的所有上电要求、即在 VDDOx 电压(3.3V 和1.8V)之前或同时、上升时间和内核(3.3V)大于6.5V/ms