主题中讨论的其他器件:LMX2594

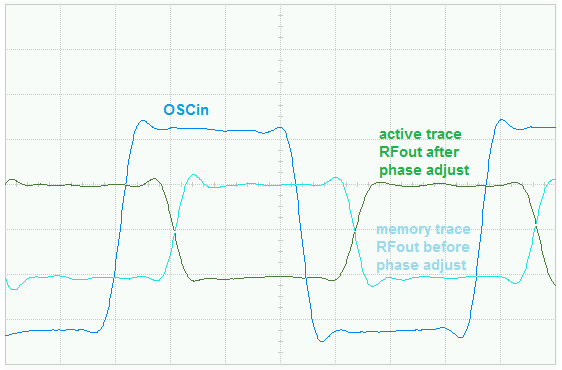

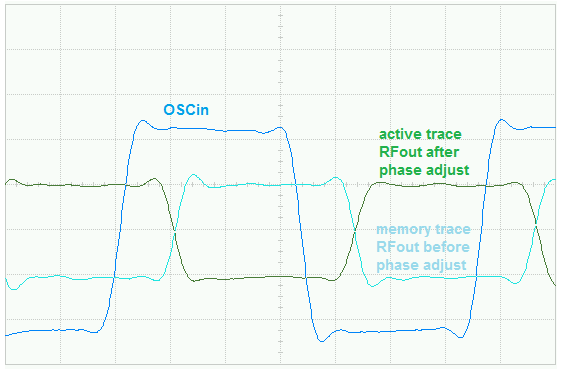

我在 LMX2594手册中了解到、可以通过改变 TICS Pro GUI 中的 MASK_SEED 变量来改变输出的相位-我已经能够在一定程度上确认该变量。 但是、我一直在尝试通过改变这个变量来实现精确的相移、但是我真的很难理解哪些参数决定分配的确切相移。

在手册的第31页上、它指出了这一点

以度为单位的相移= 360 (MASK_SEED / PLL_DEN) (IncludedDivide/CHDIV)

其中 PLL_DEN > PLL_NUM + MUS_SEED、即 MUS_SEED <= PLL_DEN - PLL_NUM。 如果违反此条件、会发生什么情况?

如果我从 TICS Pro GUI 正确解释这些变量、我 看不到任何类似的关系。 在本手册的同一页上、它似乎提出了建议(它没有清晰地写出来!) VCO_PHASE_SYNC 需要为1才能使该相移正常工作-这是真的吗? 我也不知道如何从 TICS Pro GUI 确定(或更改) FRAC_Order。

是否有人可以建议如何根据自己控制的参数确定分配的确切相移?

我希望有人能帮忙。

非常感谢、

Matthew

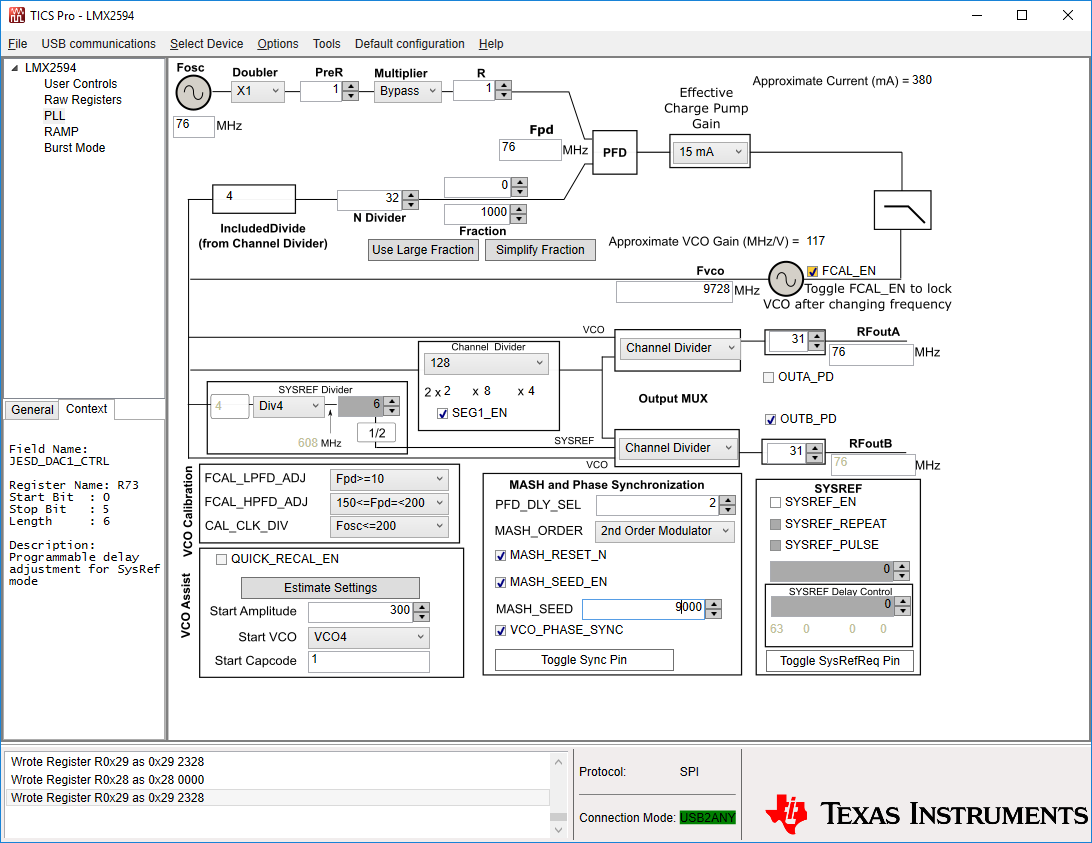

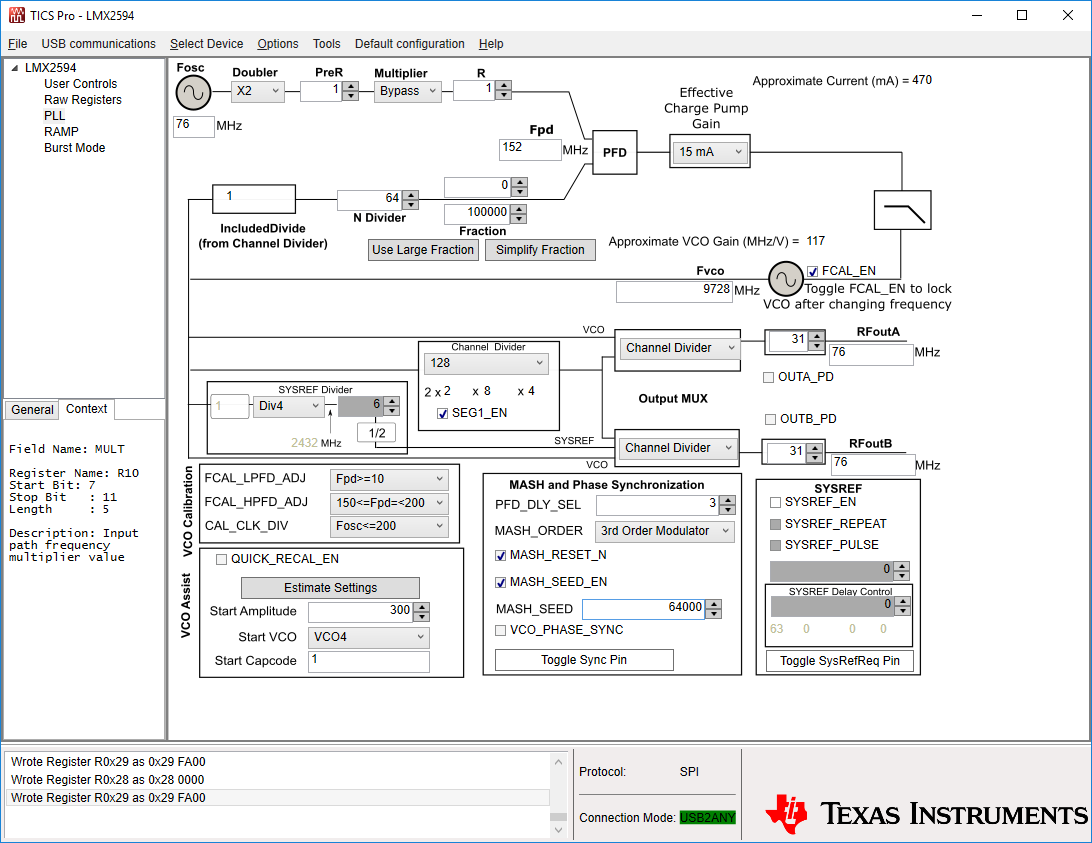

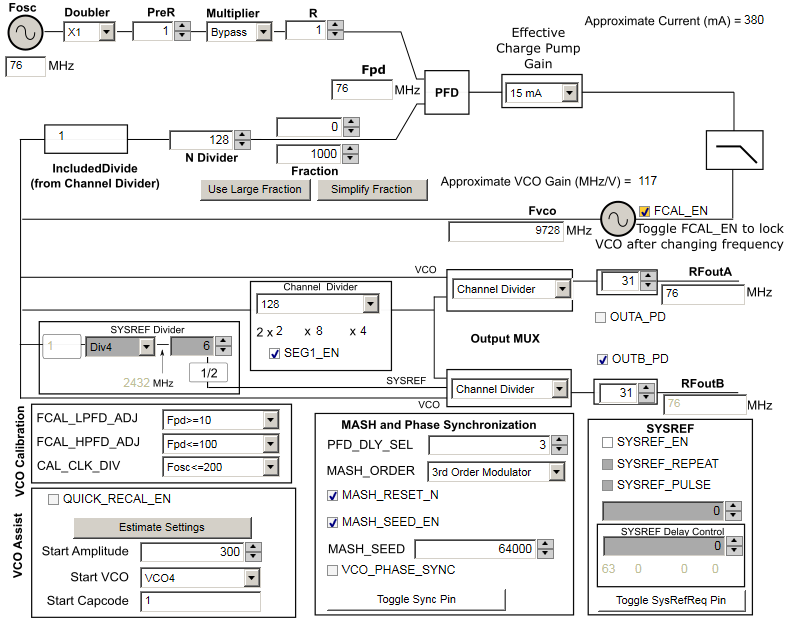

P.S. 下面的屏幕截图-在这种情况下,预期的相移应为360*(9000/1000)*(4/128)= 101.25度。 是这样吗? VCO_PHASE_SYNC 是否需要为1?