工具/软件:WEBENCH设计工具

尊敬的技术支持团队:

我想实现适当的 PLL 设置。 尤其是具有 WEBENCH 的环路滤波器。

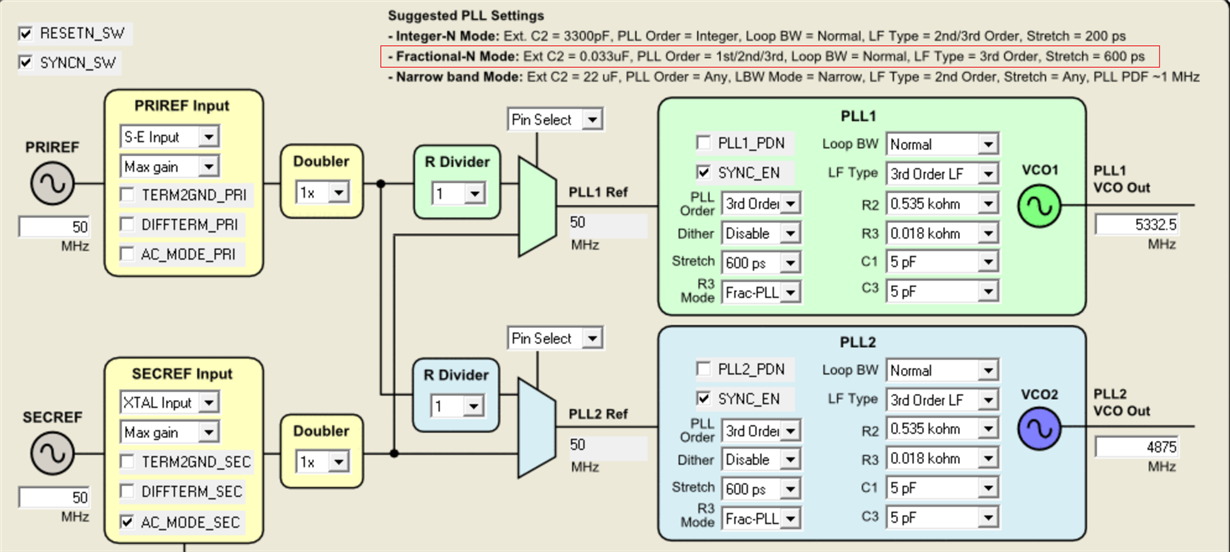

这是我的 WEBENCH 项目。

webench.ti.com/.../OpenPublicSharedProject.jsp

我 在 Webench 上将自动值更改成了 C2=33nF (环路滤波器选项卡上的基本⇒高级模式)

在可能的情况下、PLL 设置基于分数值。 因此、我应该根据下面的 Code Loader 建议选择33nF。

■问题、

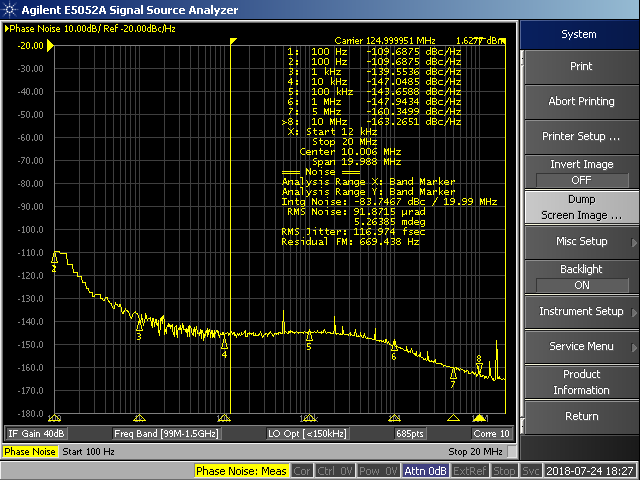

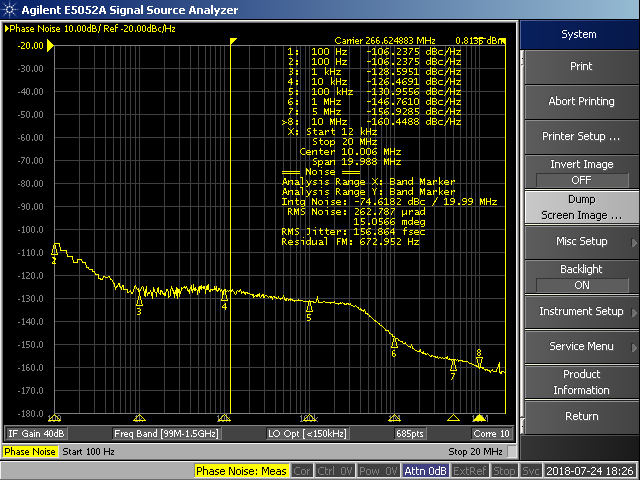

我想设置最小抖动实现。

您可以检查我的 webench 和代码加载程序吗?

如果我出错了、您能指出吗?

■我的目标时钟

输入频率:50MHz

输出频率:266.625MHz LVDS 和 125MHz LVDS

输出时钟抖动: 在10ps 峰间值内

■我的项目(Webench 和代码加载程序)

Webench

https://webench.ti.com/wb5/OpenPublicSharedProject.jsp?id=153EC8632C794927&s=c

代码加载器

(可以从.pdf 更改为.mac 吗? E2E 不接受.Mac 进行上传)

e2e.ti.com/.../4174.LMK03328.pdf

此致、

TTD