主题中讨论的其他器件: LMK04806、 LMK04832

您好、先生、

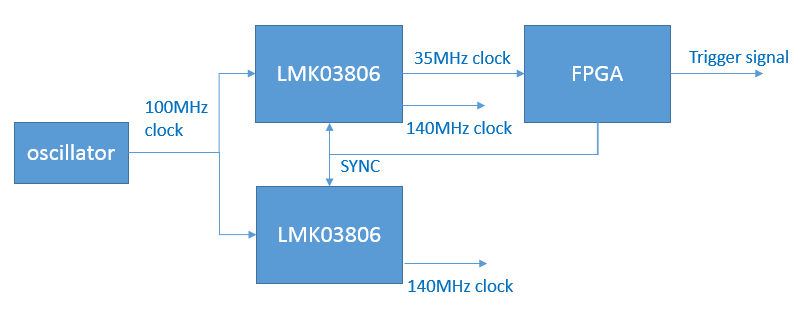

下面是我的设计图、您可以看到我使用同一 FPGA 引脚将两个 LMK03806的"SYNC"信号置为有效、因此我希望两个140MHz 时钟输出在频率和相位上同步。

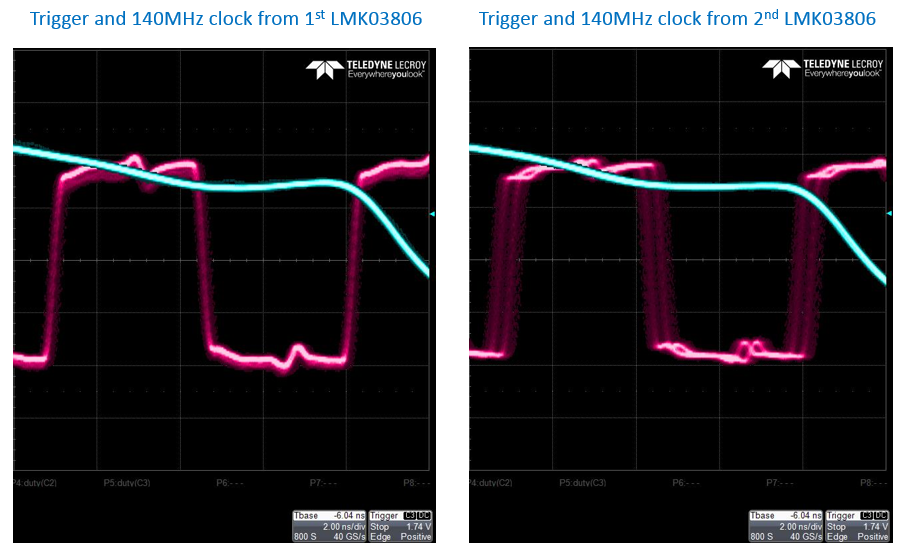

但是、当我使用 FPGA 的"触发信号"作为示波器的触发通道、并单独测量两个 LMK03806的140MHz 时钟时、我发现第一个 LMK03806的140MHz 时钟与触发信号完全同步、 不过、很明显、可以在第2个 LMK03806的140MHz 时钟上观察到~0.4ns 抖动。

由于 LMK03806内部的 VCO 设置为2500MHz、因此0.4ns 接近一个时钟周期、因此我怀疑同步机制存在问题、如果有任何方法可以解决此问题、请不胜感激、谢谢!