我发现数据表规格 VCM-AC 和 VCM-DC 令人困惑。

假设1.80V VDD_yx_YY、VCM-dc 为1.67V (1.80V - 0.13V)、输出正峰值将高于 VDD_yx_YY。 这一结论可能是由于我对规范的误解造成的。 请您澄清一下吗?

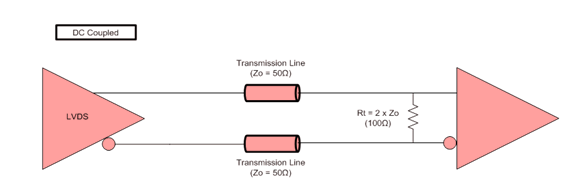

OTOH VCM-AC 规格为 VDD_yx_YY-0.76V、这意味着1.04V (VDD_yx_YY = 1.80V)。 是否有可能在数据表中交换交流和直流规格? 1.04V VCM 将允许输出驱动 LVDS 输入、而无需交流耦合。

非常感谢您的参与。