主题中讨论的其它部件:, CODELOADER

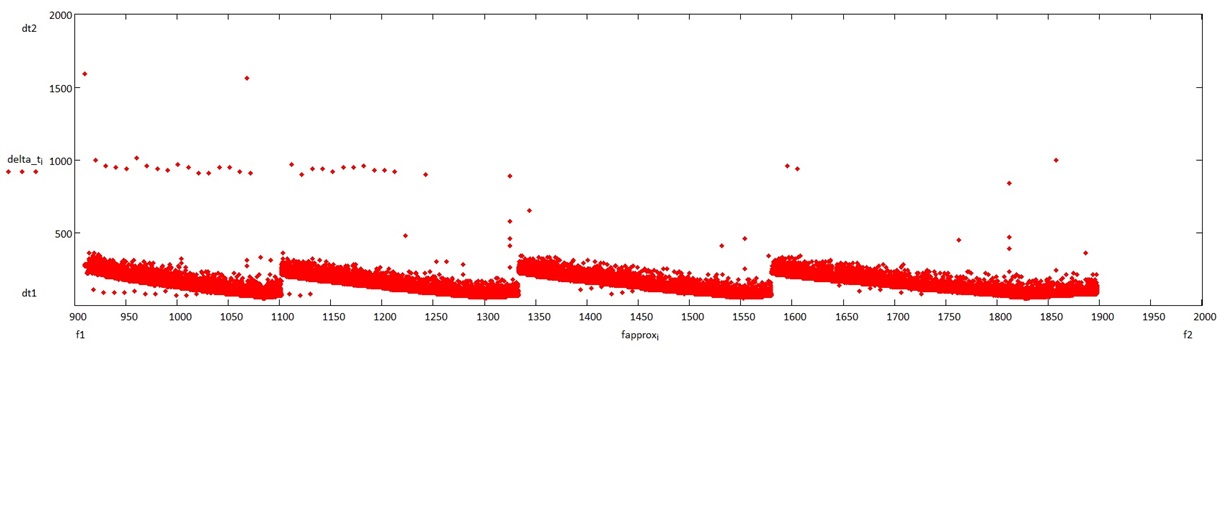

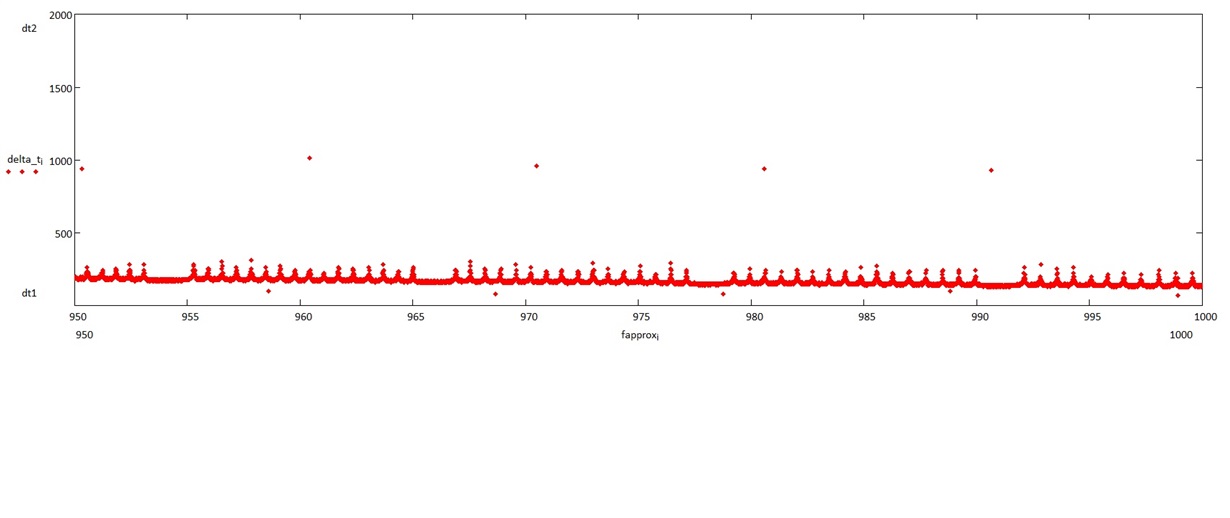

我们在较宽范围内使用 LMX2581、步长较小、f=0.9-1.8和1.8-3.6GHz、步长 df=1-2kHz。

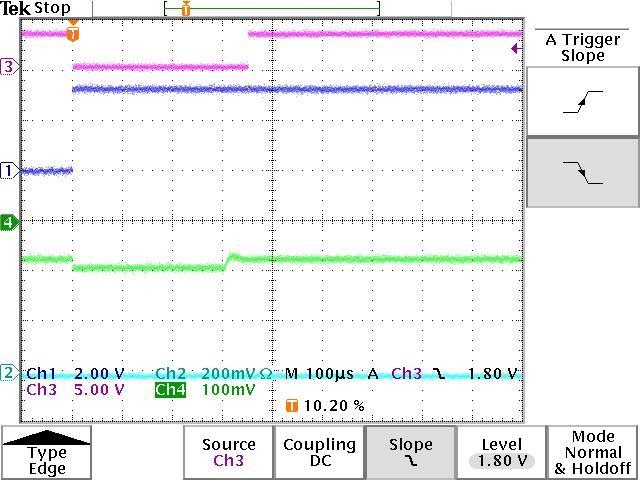

我们注意到不同的频率区域、其中 VCO 校准时间花费的时间非常长、在某些区域中为几毫秒

一个非常明显的区域、最长可达10ms!

通过我们的控制软件计算和编程的 VCO 预选、以及 CAP_CODE=47的常规锁定

时间小于100us、可在锁定检测信号中看到、当然也可在零跨度模式下使用频谱分析仪轻松看到

当"IC AUTOMUTE"功能打开时。

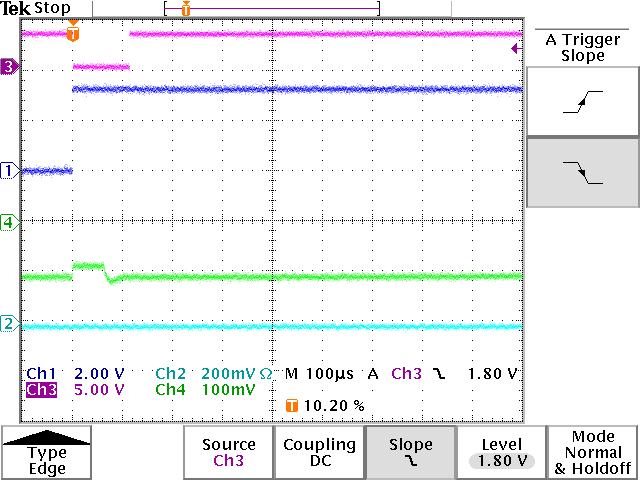

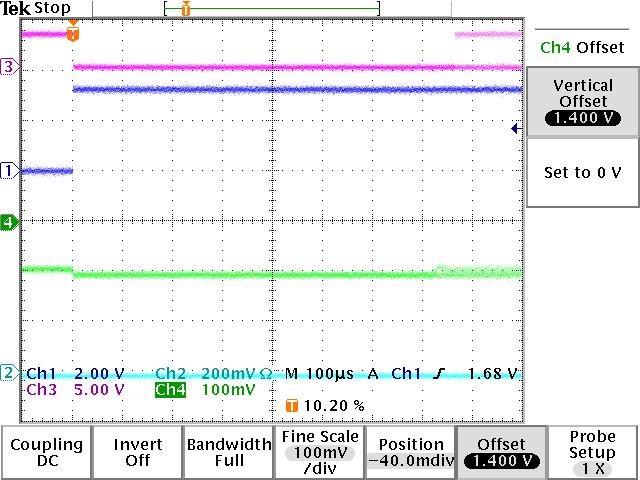

我已经使用示波器监控了调谐电压。 当 FCAal 激活时、其范围略高于1.4V

降至1.2V 左右。

根据我的观察结果、很明显、当在频率变化期间启用 FCAL 时、会向施加固定电压

VCO 调谐引脚 、即 VTune 稍微低于1.4V、并在 短时间(几个10us)内保持恒定。

临界频率范围-具有较长 FCAL 时间的频率范围恰好位于该区域、其对应位置

调谐电压也略低于1.4V。

H/W 与 EVAL 板、环路滤波器5阶、30kHz 带宽和 CPG=24非常相同。

有什么想法? 提前感谢您。

谢谢、

Konstantin

德国德累斯顿