请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

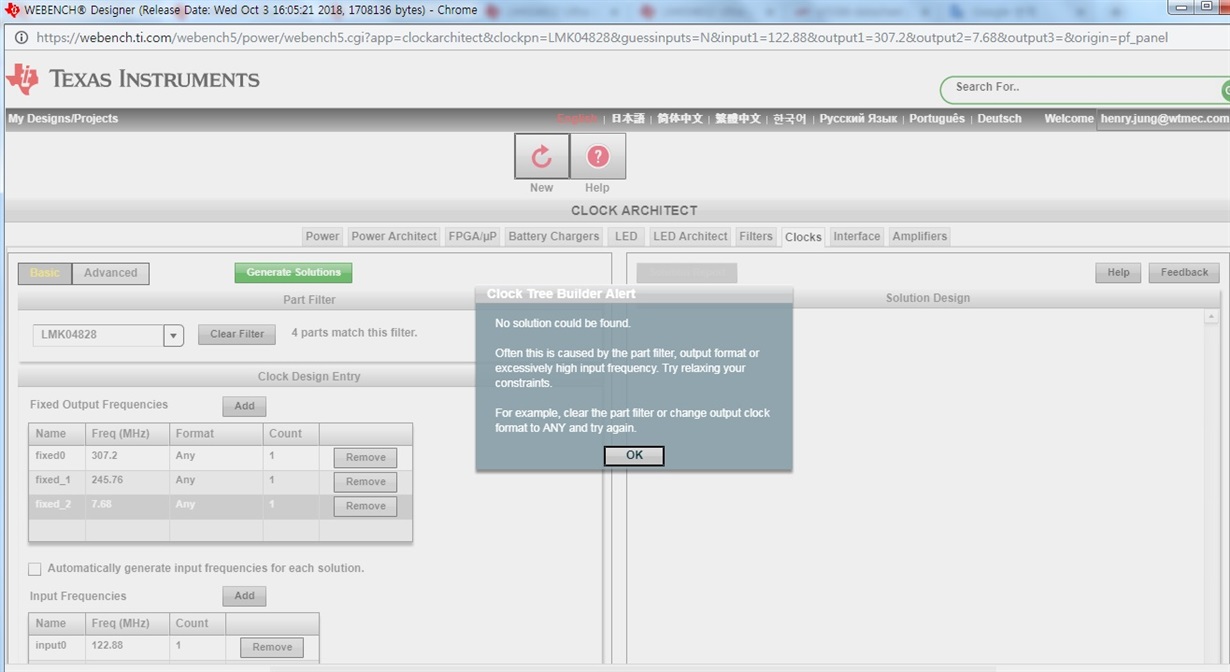

器件型号:LMK04828 工具/软件:WEBENCH设计工具

设计。

LMK04828产品的设计审查。

我们的概念如下。

LMK04828 webench 不支持?

参考时钟(VCXO 或 TCXO):122.88Mhz

LMK048xx 输出时钟

FPGA (CPRI):307.2Mhz

2. DAC、ADC:245.76Mhz

SYSREF 范围:3.84Mhz 至30.72Mhz

谢谢你。