主题中讨论的其他器件:LMX2572、 PLLATINUMSIM-SW、 LMX2594

我使用的是 LMX2572评估板。 以下是所面临的问题

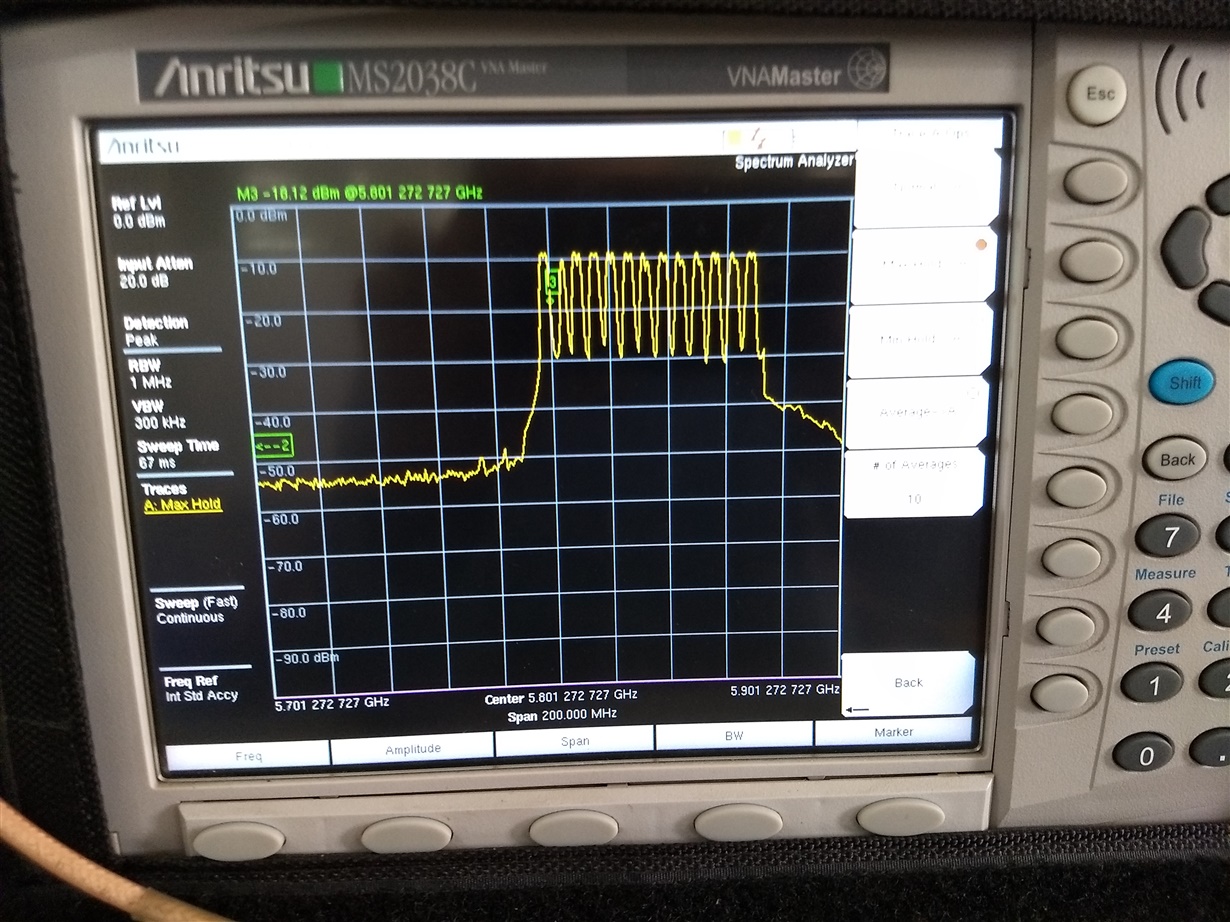

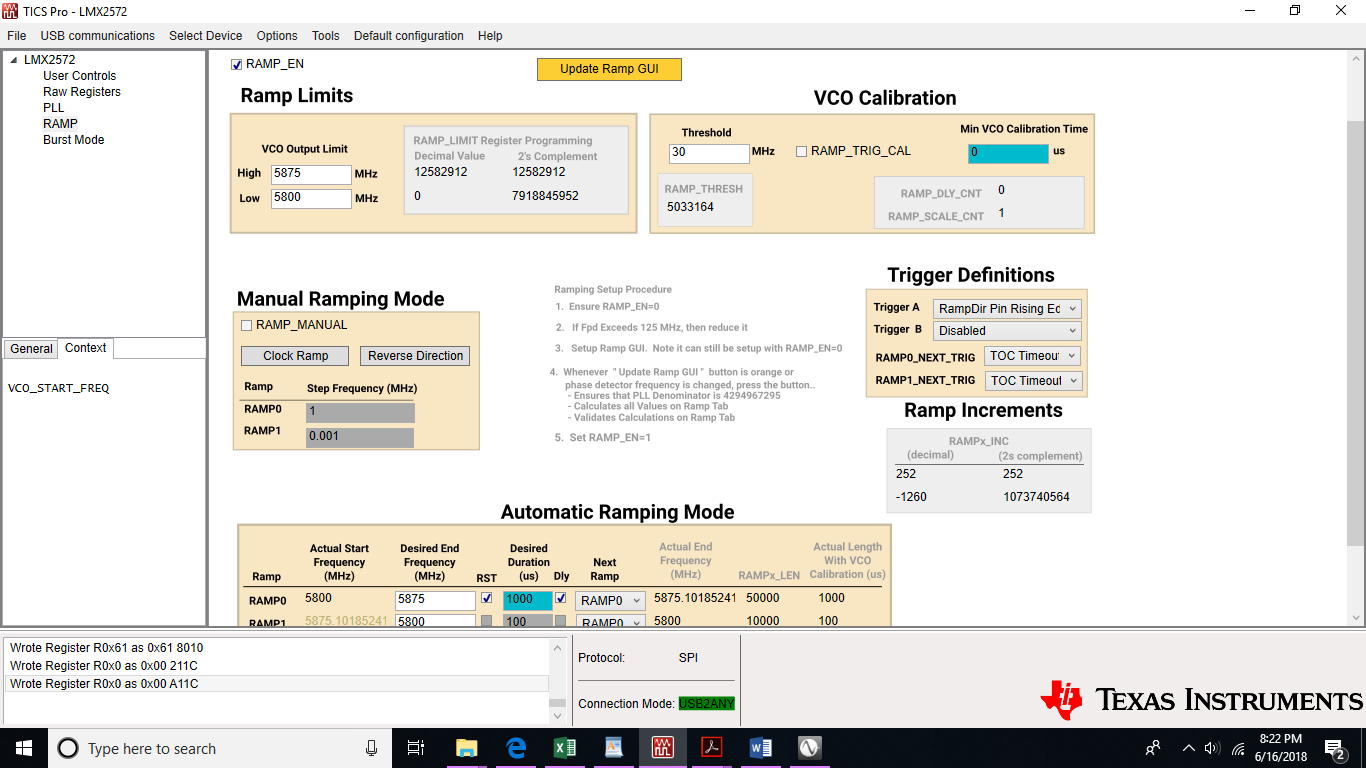

我们的应用是在锯齿自动斜坡模式下以>1ms 的时间运行评估板。 我们正在扫描雷达应用的5800-5900MHz。

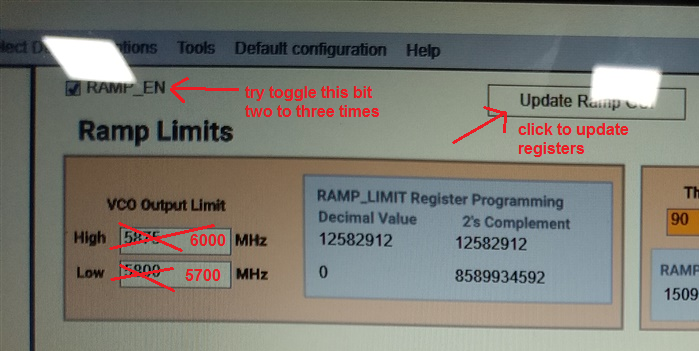

扫描未正确进行、连接的是斜坡设置屏幕截图供参考

PLL 在环路滤波器值为1MHz 时不稳定:

C1_LF:15pF

C2_LF:450pF

R2_LF:2.5k

R3_LF:0

C3_LF:DNP (开路)

R4_LF:0

C4_LF:DNP (开路)

除此之外、

R16、R19、R20:0欧姆(短路)

我们已经尝试更改环路滤波器值、即使在更高的带宽下、PLL 也不稳定。

我需要一种解决方案、以便在锯齿波斜坡模式下尽快实现稳定的 PLL 输出和5800-5900MHz 范围内的扫描。

此致、

Suresh