您好 、Timothy T / e2e.ti.com/.../4798065

我们有一个基于 LMK04828的电路板、我们正在尝试在 SYSREF 分配路径上实现 SYSREF 脉冲发生器、

案例1:

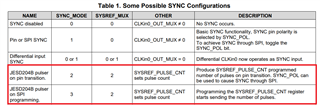

- CLKIN0- 5MHz 外部信号、OSCIN 上的100MHz VCXO、SYSREF_MUX 设置为 SYSREF_Pulser (CLKIN0)

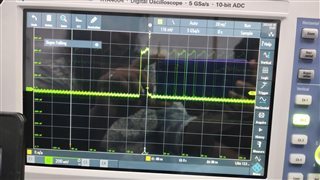

我们观察到以下 SYSREF 分布路径上的奇怪输出是 SYSREF 和配置文件捕获波形的附加图像:

- 多个 SYSREF、是非周期性输出

- SYSREF_Pulser 计数为2、我们已尝试检查 SYSREF_PD 集、但仍观察到相同的情况。

- 当 SYSREF_MUX 设置为 SYSREF 连续但不在脉冲发生器模式时、我们会观察到适当的 SYSREF

- 我们不使用同步路径。

。

LMK 配置文件: e2e.ti.com/.../secondary_5F00_lmk.txt

请告诉我们、我们在这里遗漏的任何内容。

CASE2:我们在 CLKIN0处观察到同样的情况、即 CLKIN0保持断开状态、SYSREF_MUX 设置为 SYSREF_Pulser。