您好!

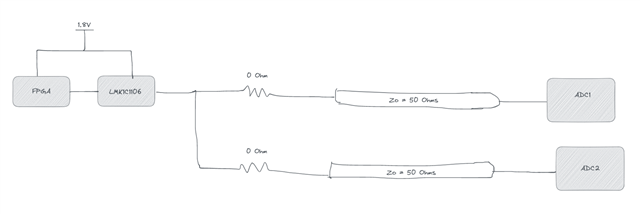

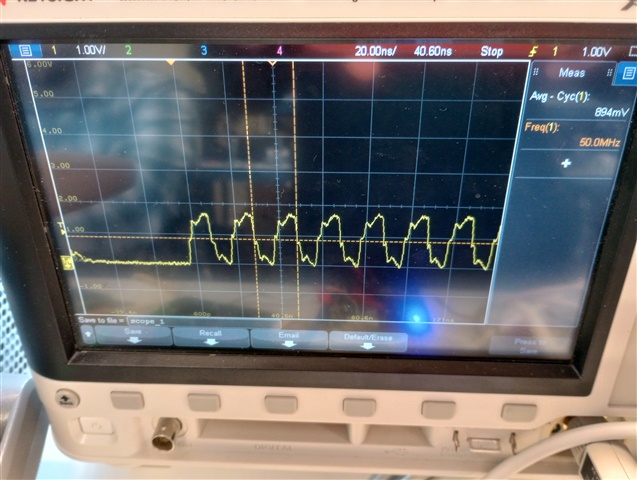

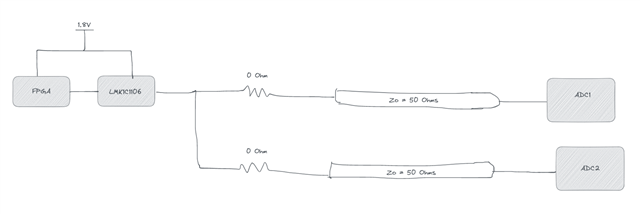

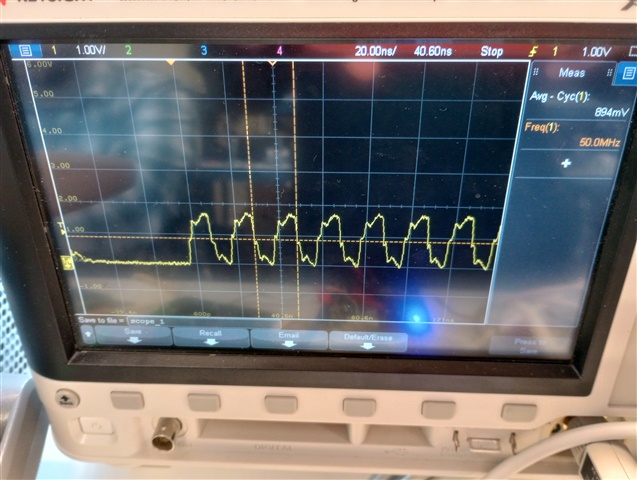

我们有新的电路板、50MHz SPI 时钟(用于 ADC)看起来不正确-看起来有点过阻尼、这很奇怪、因为我们尚未添加任何串联电阻。 我实际上希望有一些振铃。 请参阅其中一个 ADC 的基本原理图和示波器(布线长度为~6英寸)。 探针具有低电感(无接地引线)、接地非常靠近 ADC 时钟输入。 示波器是1GHz 示波器。 您对可能发生的情况有什么建议吗? 我们的 PCB 布线已调整为50欧姆特性阻抗(Zo)。 ADC 输入仅为 HiZ (无终端)。

感谢您提供的任何帮助!

Erik

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们有新的电路板、50MHz SPI 时钟(用于 ADC)看起来不正确-看起来有点过阻尼、这很奇怪、因为我们尚未添加任何串联电阻。 我实际上希望有一些振铃。 请参阅其中一个 ADC 的基本原理图和示波器(布线长度为~6英寸)。 探针具有低电感(无接地引线)、接地非常靠近 ADC 时钟输入。 示波器是1GHz 示波器。 您对可能发生的情况有什么建议吗? 我们的 PCB 布线已调整为50欧姆特性阻抗(Zo)。 ADC 输入仅为 HiZ (无终端)。

感谢您提供的任何帮助!

Erik

您好 Erik、

我认为这可能来自这些引脚上的电容负载。 我看到 ADC 的数字输入具有2pF 的输入电容。 迹线电容也很重要。 FR4材料的一般经验法则是每英寸布线长度约2pF。 在布局中、您有两个单独的迹线、还是只有一个迹线、然后它进入两个 ADC? 它看起来像是电阻器之后的两条单独走线、因此每条走线也会产生大约12pF 的电容。

如果使用两个 ADC、则可以根据布线长度在器件上加倍 pF 负载。 这可能会导致信号减慢。

放置一个串联电阻器将有助于在更高频率下实现这种失真。 我们可以从10欧姆开始、以避免摆幅减小得过大、并使其保持在 ADC 的可接受范围内。

最棒的

阿西姆