主题中讨论的其他器件:TIDA-01021、 LMK61E2、

大家好、:

我对 LMK04828B 中 PLL1的数字锁定有疑问。

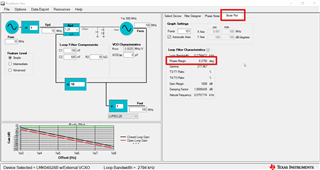

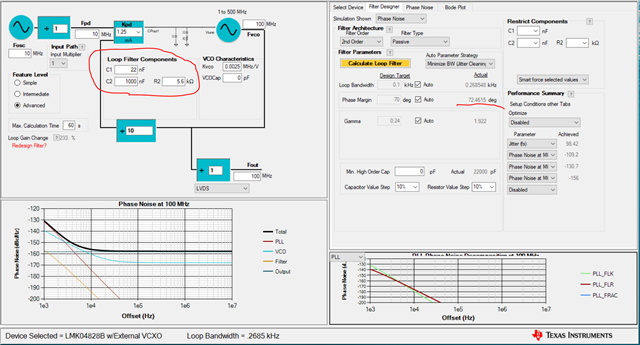

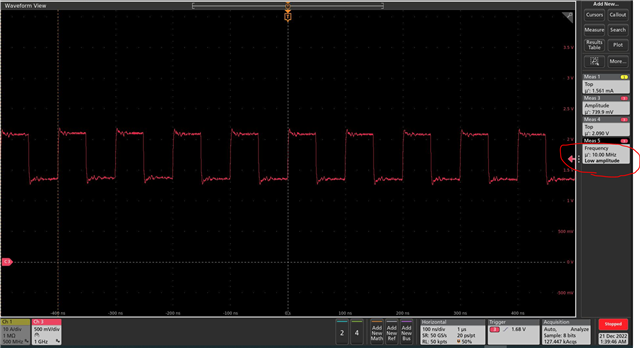

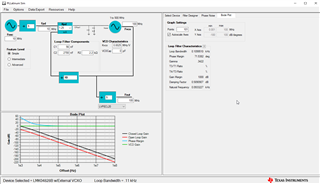

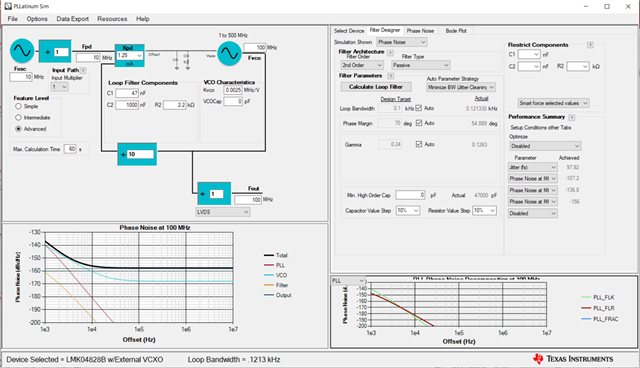

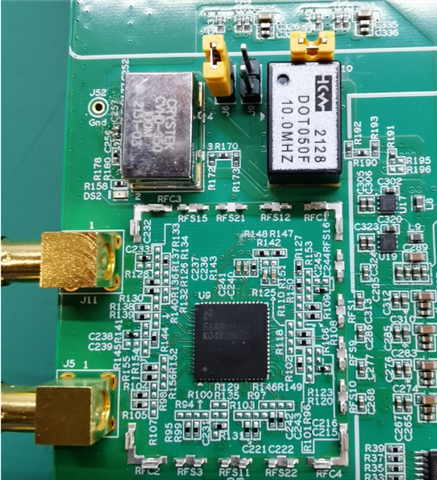

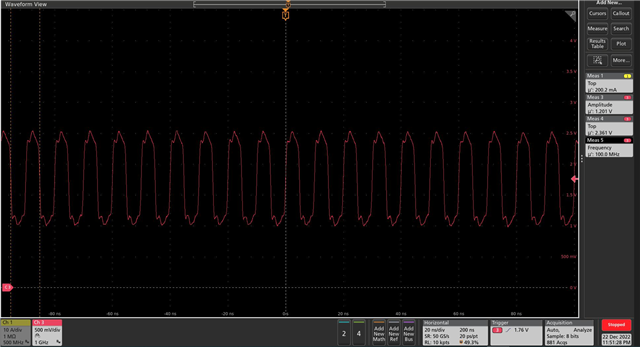

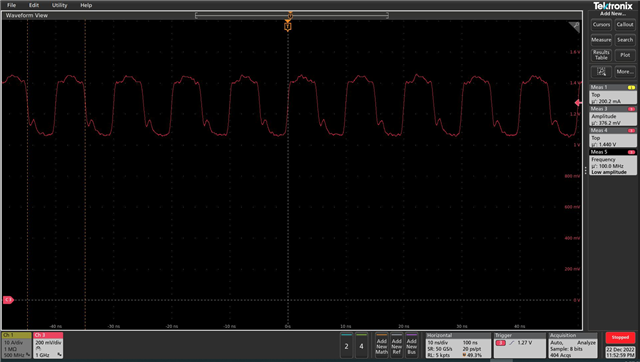

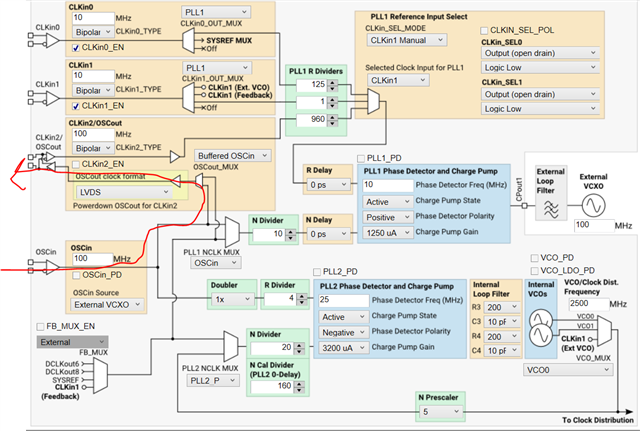

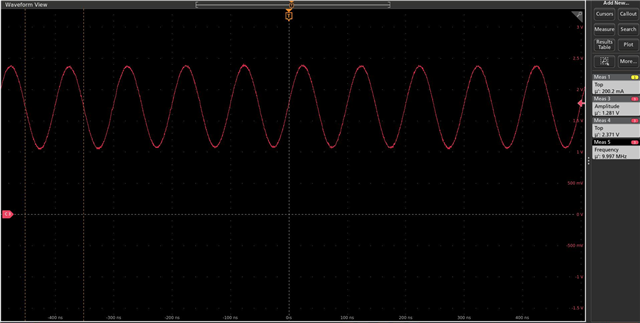

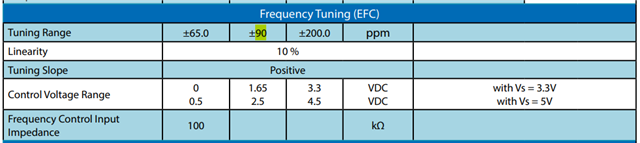

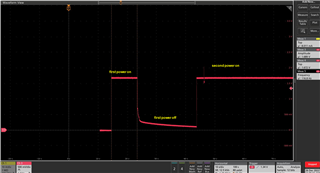

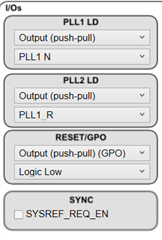

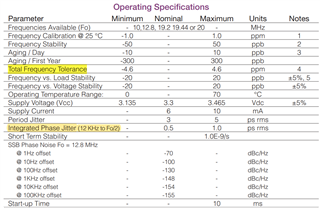

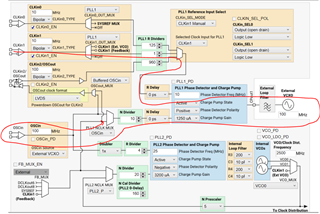

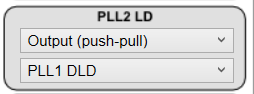

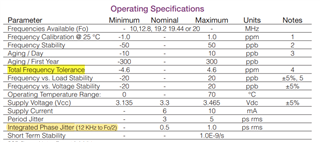

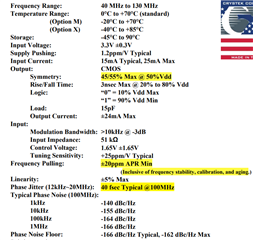

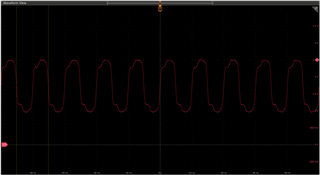

如下图1所示、我在 TCXO 和 CLKin1之间提供10MHz 的频率、FPD 设置为10MHz、外部 VCXO 设置为100MHz、这与 TIDA-01021上的 VCXO 相同。 用于 PLL1 DLD 的 LED 不能变亮、但当该 LED 切换到 PLL2 DLD 时、 它将变亮。 图2是10MHz TCXO 的参数、图3是100MHz VCXO。 我还测试了 LMK04828B 从 VCXO 到 OSCin 的100MHz、如下图4所示、没关系。 回路滤波器中的容量和电阻器也与 TIDA-01021设计相同(c1=0.1uF、c2=0.68uF、r2=39k Ω)

我还注意到"10.2数字锁定检测频率精度"、 因此尝试将 PLL1_DLD_CNT 从8192更改为5000、并将 PLL1_WND_SIZE 保持为43ns。 但它不起作用。

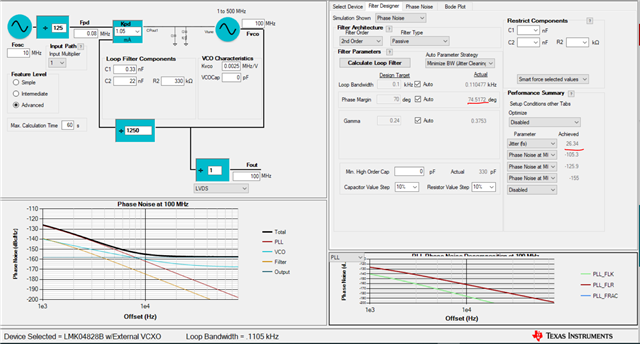

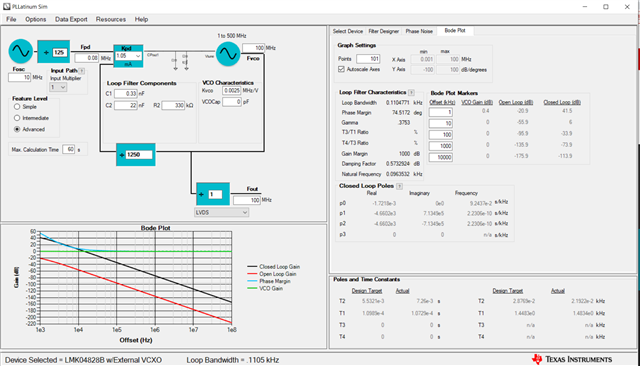

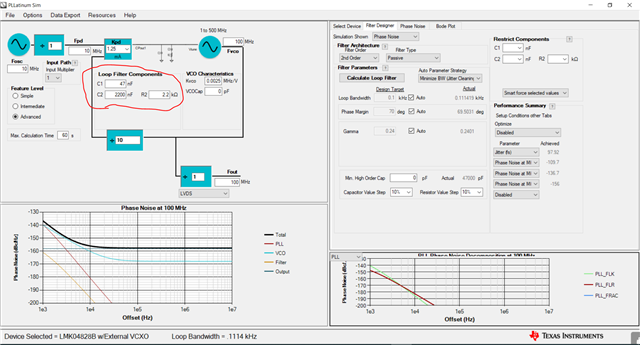

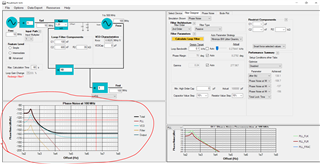

最后、我使用 PLLatinum Sim 根据上面的环路滤波器来仿真 PLL1、相位噪声曲线似乎不是很好。

请帮我检查我的设置有什么问题? 或者指出正确的方法来锁定 PLL1?

提前感谢!

图1.

图2.

图3.

图4.

图5.

此致!

Jason