您好!

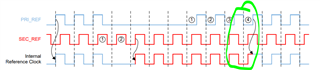

1.在数据表图43中、当基准输入从次级侧自动切换到初级侧时、PLL 是否会解锁?

图44中的流程图描述了当主输入无效时、当多路复用器自动切换到辅助输入时、PLL 应立即解锁。 当主输入有效时、多路复用器自动切换到主输入、然后 PLL 锁定到主输入。 在 PLL 锁定到主输入之前是否会发生一个短 PLL 解锁事件?

如果 R51.2设置为1、则在自动切换过程中不会看到任何 PLL 解锁事件。 因此、如果次级输入可用、并且 R51.2为1。 我不再需要担心 PLL 解锁事件、对吧?

2.在表8中,14号状态为“PLL secondary to primary switch in automatic mode”(PLL 从辅助到主开关处于自动模式)。 这是什么? 状态引脚在多路复用器自动切换到主输入后是否生成脉冲? 如果是、脉冲持续多长时间?

![]()

此致、