主题中讨论的其他器件:LMK61E2、

大家好、

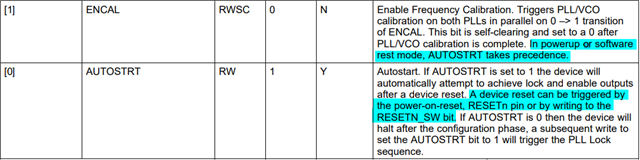

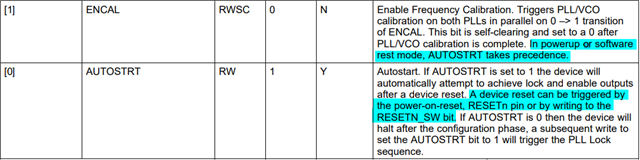

这些寄存器位(SWR2PLL、自动启动和 ENCAL)的功能是什么? 如何使用它们?

自动开始位和 ENCAL 位是否都具有触发 PLL 锁定的功能?

对于 ENCAL 位、什么是软件休息模式?

器件没有 RESETn 引脚和 RESETN_SW 位、 用户如何使用 AUTOSTRT 位?

您是否可以租赁留言? 提前感谢。

此致、

罗美

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

这些寄存器位(SWR2PLL、自动启动和 ENCAL)的功能是什么? 如何使用它们?

自动开始位和 ENCAL 位是否都具有触发 PLL 锁定的功能?

对于 ENCAL 位、什么是软件休息模式?

器件没有 RESETn 引脚和 RESETN_SW 位、 用户如何使用 AUTOSTRT 位?

您是否可以租赁留言? 提前感谢。

此致、

罗美

客户的具体疑问是:

如果自动启动设置为1、

修改输出频率125MHz->100MHz:写入 PLL 寄存器配置 OUTDIV ->设置 SWR2PLL=1 ->锁定

2.修改输出频率100MHz->125MHz:将 PLL 寄存器配置写入 OUTDIV ->设置 SWR2PLL=1 ->输出频率不正确、PLL 失锁->再次设置 SWR2PLL=1 ->锁定

3.修改输出频率100MHz->125MHz:写入 PLL 寄存器配置 OUTDIV ->设置 SWR2PLL=1 ->输出频率不正确、PLL 失锁 ->设置 ENCAL=1 ->输出频率不变、PLL 失锁。

为什么上面的1和2个输出具有不同的锁定状态?

当自动启动设置为0时、

修改输出频率 125m->100M:写入 PLL 和 OUTDIV -> SWR2PLL=1 ->无时钟输出->自动启动=1或 ENCAL=1 ->锁定

2.修改输出频率 100M->125m:写入 PLL 和 OUTDIV -> SWR2PLL=1 ->无时钟输出->自动启动或 ENCAL=1 ->锁定

您好、Amy、

我看到数据表中有一些奇怪的语句(例如、不存在 RESETn 引脚、即使该器件只有一个 PLL、也提到了两个 PLL)。 可能会弃用包含 ENCAL 和 AUTOSTRT 位的寄存器 R10 (DEV_CTL)、不建议客户使用。 我目前还没有使用工程工具访问 ENCAL 和 AUTOSTRT 的方法、因此现在我无法在实验中测试与这些工具相关的问题。

SWR2PLL 位复位 VCO 校准和时钟分频器、我认为它应该在对 PLL 设置进行更改后被写入、但我还不知道具体细节。

我在包含 LMK61E2的 EVM (器件略有不同、但使用相同的寄存器映射)的实验中使用100MHz <--> 125MHz 和 SWR2PLL 测试了该问题。 我无法复制"修改输出频率100MHz->125MHz:使用 OUTDIV 写入 PLL 寄存器配置->设置 SWR2PLL=1 ->输出频率不正确、PLL 失锁->再次设置 SWR2PLL=1 ->锁定"行为。 我注意到、当我写入输出分频器寄存器并在之后触发 SWR2PLL 时、输出频率发生变化、不会打破锁定或产生持续不正确的输出频率。 我确实注意到、在触发 SWR2PLL 后的很短的时间内很少会出现不正确的输出频率、但它会立即自行纠正。

我正在与我的团队核实 R10寄存器的状态、并查看他们是否对我无法重复的粗体问题有更多想法。 客户是否知道该问题发生的频率?

谢谢、

苏伊文

您好 Evan、

非常感谢。

以下是我从 客户那里收到的信息:

这种现象发生在100%频率下、采用特定配置、我在4个芯片上进行了测试、结果都是一样的。 我使用以下配置修改了频率不仅 OUTDIV、而且与 PLL 相关的配置:未标记的寄存器使用数据表中的复位值。 如果需要、我可以提供我配置为使用的 Linux Sheel 脚本。

100MHz

| 地址 | 21. | 23 | 26 | |

| 值 | 0x03 | 0x2E | 0x2E |

125MHz

| 地址 | 21. | 23 | 26 | |

| 值 | 0x03 | 0x28 | 0x32 |

此致、

Amy

您好、Amy、

我了解 到、寄存器 R10继承了旧产品、通常不应有客户对其进行编程的理由。 默认情况下、器件的 EEPROM 具有 AUTOSTRT = 1、因此器件将在上电后以及通过 SWR2PLL 位手动触发软件复位后自动校准其 VCO、这是通常所需的行为。 ENCAL 会手动触发 VCO 校准、但我认为使用 SWR2PLL 更有意义、SWR2PLL 存在于完全支持的寄存器 R72中。

我今天使用您提供的信息运行了实验室中的一些测试。 首先、我将器件配置为使用0x2e 的 N 分频器(因此 VCO 频率为4600MHz)和0x2e 的输出分频器正确输出100MHz HCSL 信号。 我将0x28写入 R23以更改输出分频器、输出信号如预期的那样变为4600MHz/40=115MHz。 然后我将0x32写入 R26、将 N 分频器更改为十进制的50、输出信号按预期偏离至大约116.42MHz (尚未允许 PLL 重新校准)。 最后、我将0x02写入 R72以触发 SWR2PLL 软件复位、并立即出现125MHz 的正确输出频率。 因此、我再次无法重现此问题、因为我在第一次 SWR2PLL 复位后实现了稳定的125MHz 输出。

我认为这将有助于为客户提供配置代码、我想检查下一周的初始寄存器配置和后续写入。

谢谢、

苏伊文

您好 Evan

我是 Amy 提到的客户。Linux shell 和 U-boot 驱动程序。都有此问题

这是我使用的 Linux shell 脚本。您可以将其另存为.sh 文件并使用它。

默认情况下、它使用 i2c 端口0、您可以配置 i2c_index 环境变量来更改它。

以下是参数:

-f $value (100或125):将频率更改为100或125 MHz。

-r:将寄存器设置为复位值。

s:将寄存器保存到 EEPROM。

#!/bin/bash

i2c_index=${I2C_INDEX:="0"}

dcxo_addr=${DCXO_ADDR:="0x59"}

outdiv_by0_100m='0x2e'

pll_n_by0_100m='0x2e'

pll_lf_r2_100m='0x04'

outdiv_by0_125m='0x28'

pll_n_by0_125m='0x32'

pll_lf_r2_125m='0x08'

# Reset to default value

reset() {

i2ctransfer -y $i2c_index w2@$dcxo_addr 10 0x01

i2ctransfer -y $i2c_index w3@$dcxo_addr 16 0x00 0x00

i2ctransfer -y $i2c_index w20@$dcxo_addr 21 0x01 0x00 0x20 0x00 0x00 0x64 0x00 0x00 0x00 0x00 0x00 0x00 0x0c 0x24 0x03 0x08 0x00 0x00 0x00

i2ctransfer -y $i2c_index w2@$dcxo_addr 42 0x00

i2ctransfer -y $i2c_index w2@$dcxo_addr 49 0x10

}

# Set output clock

set() {

i2ctransfer -y $i2c_index w2@$dcxo_addr 21 0x03

i2ctransfer -y $i2c_index w2@$dcxo_addr 23 $1

i2ctransfer -y $i2c_index w2@$dcxo_addr 26 $2

i2ctransfer -y $i2c_index w2@$dcxo_addr 36 $3

i2ctransfer -y $i2c_index w2@$dcxo_addr 72 0x02

}

# Save to EEPROM

save() {

i2ctransfer -y $i2c_index w2@$dcxo_addr 49 0x50

sleep 0.2s

i2ctransfer -y $i2c_index w2@$dcxo_addr 56 0xbe

i2ctransfer -y $i2c_index w2@$dcxo_addr 49 0x12

sleep 0.2s

i2ctransfer -y $i2c_index w2@$dcxo_addr 56 0xbe

i2ctransfer -y $i2c_index w2@$dcxo_addr 49 0x11

sleep 0.2s

i2ctransfer -y $i2c_index w2@$dcxo_addr 56 0x00

}

while getopts :f:sr argv ; do

case $argv in

f)

if [ $OPTARG -eq 100 ] ; then

set $outdiv_by0_100m $pll_n_by0_100m $pll_lf_r2_100m

elif [ $OPTARG -eq 125 ] ; then

set $outdiv_by0_125m $pll_n_by0_125m $pll_lf_r2_125m

else

echo "Invalid freqency"

fi;;

s) save;;

r) reset;;

[?]) echo "invalid option or miss option argument";;

esac

done

此致、

张蓝

您好、蓝、

我是假期回来的。 感谢您提供该代码、我正在查看该代码、如果我发现任何异常情况、我将很快通知您。

顺便说一下、只需更改输出分频器值(寄存器 R23)、就可以在100MHz <--> 125MHz 之间切换。 例如、如果我们将 VCO 配置为仅在5000MHz 下运行(寄存器 R26 = 0x32)、十进制的输出值50会产生100MHz 的输出、十进制的40会产生125MHz 的输出。 这是我在2月16日所做的、避免了更改 VCO 频率、因此不需要进行软件复位来重新校准 VCO。 唯一的潜在缺点是、在 VCO 频率= 5000MHz 时、125MHz 输出的相位噪声性能可能与在 VCO 频率= 4600MHz 时略有不同、但可能适合您的应用。 我仍在调查失锁行为、因为这是奇怪和意外的、但这是一种可能的解决方法。

谢谢、

苏伊文

您好、蓝、

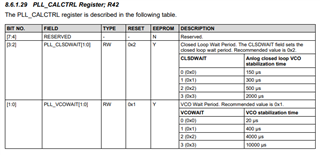

我研究了 RESET()函数的代码,并注意到一行代码异常。 它看起来是在向寄存器 R42写入0x00。 R42包含两个 VCO 校准设置。

R42在我的内部 GUI 中隐藏、因此我假设我们不打算让客户修改它。 将其写入0x00会将模拟闭环稳定时间和 VCO 等待时间设置为其最小值、这不建议这么做、并且可能不会在您启动软件复位后为 VCO 提供足够的时间来正确重新校准。 如果在更改输出频率之前的任何时候运行 reset(),或者如果该寄存器值已写入 EEPROM,则可能是导致您发现问题的原因。

我认为基于数据表说明的 R42建议/默认值应为0b00001001 = 0x09。 尝试将其写入 R42、并告知我们它是否解决了失锁问题。 如果确实如此、请确保 R42在 EEPROM 中具有正确的0x09值、并避免在将来对其进行编辑。

谢谢、

苏伊文

您好 Evan、

感谢您的支持。

我测试并更改了 R42值、它解决了问题。

但是、我发现在数据表中、稳压器映射和稳压器描述具有不同的复位值、两个值都不输出70.656MHz 的默认频率、并且稳压器映射值甚至超过 PLL 输出频率的上限。

这里是我发现的差异

|注册| 17 | 26 | 34 | 36 | 42 |

|--- |---|---|---|---|---

|寄存器映射复位 val | 0x00 | 0x64 | 0x24 | 0x28 | 0x00 |

|寄存器说明复位 val | 0x80 | 0x32 | 0x28 | 0x08 | 0x09 |

此致、

张蓝