主题中讨论的其他器件:CLOCKPRO

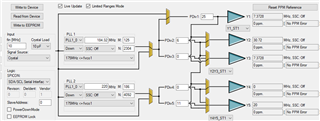

我正在使用您的时钟专业版1.2.1软件来从10MHz 输入时钟生成三个时钟20MHz、7.3728Mhz 和30.72MHz、软件选择 CDCE925pwr 芯片并将这三个信号分配给 Y5、Y3和 Y1、误差全部为0ppm。 例如、7.3728MHz 分配给 Y3 、包含"0 ppm"和"无 PPM 错误"消息、但如果我将 PDIV2也设置为25、与 PDIV3相同、Y2更改为7.3728MHz 、但其下的消息是"无限 ppm "和"0"、这是否意味着 Y2也具有0ppm 误差?

如果我使用软件向导来生成四个 时钟20MHz、7.3728Mhz 和30.72MHz、7.3728MHz、软件可以从同一源同时生成30.72Mhz 和7.3728MHz、而不是同时生成两个7.3728MHz、有什么特别的原因吗? 谢谢。