Other Parts Discussed in Thread: LMK00804B

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK00804B 大家好、

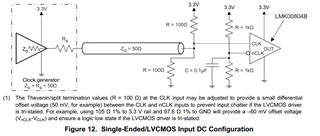

在 TI 的4xAWR2243级联成像雷达参考设计 TIDEP-01012参考设计| TI.com 中、LMK00804B 的 nCLK 输入通过以下电阻梯设置为直流偏置至0.7V:

40M_BUF_ IN_ PRIMAWRY 时钟来自 AWR_1_OSC_CLKOUT、该时钟的摆幅为1.4V 方波。

我对输入直流偏置几乎一无所知、 为何同相差分时钟输入不是直流偏置至0.7V? 难道不是 两个差分时钟输入都是直流偏置的吗?