Other Parts Discussed in Thread: LMK1D1204

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

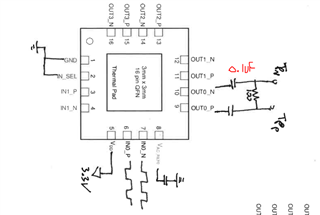

器件型号:LMK1D1204 我正在试验电路板上测试 LMK1D1204 LVDS 时钟缓冲器、以确定该缓冲器是否适用于相应设计。 我使用3.3V 的 VDD 并输入 0-2V 的差分时钟信号、但输出在0.1uF 电容器之前处于0.5V 的稳定状态、在电容器之后处于0V。 以下是我们尝试的配置。 目前、我们不关心噪声、因为这只是一个简单的"是否会起作用"测试。 悬空输入(IN1_P 和 IN1_N)是否会激活失效防护功能?