主题中讨论的其他器件:、 LMX2820、 LMX2595、 LMX2594、LMX2572

您好!

我们计划在中使用 LMK04832 单环路0延迟模式 对于我们有严格相位噪声要求的应用、

配置如下、

OSCin:从中删除了100MHz 极低相位噪声(-130dBc @ 100Hz) TTL Sqaure Wave 的 OCXO

VCO1:3200MHz

OUT1:100MHz @ LVPECL1.6

OUT2:1600MHz @ LVPECL1.6

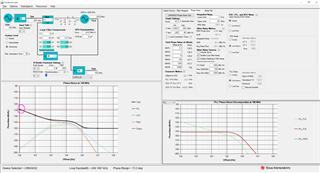

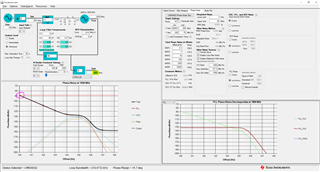

OUT3:400MHz @ LVDS

在 PLLatinum sim 软件中仿真输出100MHz 相位噪声时、在100Hz 偏移时观察到-4dB 的相位噪声下降、如下所示。

查询:

由于相位噪声对我们的应用至关重要、请确认使用 LMK04832时相位噪声降级是否不会超过-4dB 降级 i.e、-126dBc/Hz @ 100Hz 偏移? 或者实际实施是否会引起额外的性能下降?

是否有更好的器件可以在较低偏移(<10kHz)下提供更低的相位噪声降级并具有0延迟功能和 Sysref 生成功能?

提前感谢、

Deva.