Other Parts Discussed in Thread: LMK03033, LMK03000, LMK01000

主题中讨论的其他器件:LMK03033,, LMK01000

您好!

我们将使用5 LMK03033扇出时钟、从而扇出到16个 ADC 芯片和4个 FPGA。 架构如下所示:

Source > LMK #1 > LMK #2 > ADC (4x)+ FPGA

> LMK #3 > ADC (4倍)+ FPGA

> LMK #4 > ADC (4x)+ FPGA

> LMK#5 > ADC (4x)+ FPGA

源频率为50MHz、LMK#1 为 LMK2-5生成125MHz (LVDS)、为 ADC 生成250MHz (LVPECL)、为 FPGA 生成125MHz (LVDS)。 LMK 指示它们已锁定(LD 引脚为高电平、寄存器编程为高电平=锁定)。 对 LMK 寄存器进行编程后,对 SYNC*应用脉冲。 首先对 LMK #1进行编程,然后(当前在等待6s 后)同时对 LMK #2-5进行编程。 在此应用中、我们通过插值数字脉冲来测量数字化 ADC 脉冲到达次采样精度的时间。 同时生成并使用不同通道进行数字化的脉冲应具有零+/-测量精度 X 的到达时间差。例如、馈送到 ADC#1和 ADC#2 (均由 LMK#2计时)的分离脉冲发生器信号显示 X =~50ps。

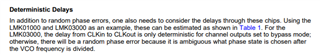

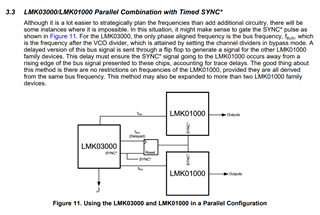

然而、对于由不同 LMK 计时的2个通道、X =~1200ps (例如由 LMK#2计时的 ADC #1和由 LMK#3计时的 ADC #5)。 在所有其他相等的条件下、我们认为这是由于多个 LMK 芯片之间的时钟同步比单个芯片内的时钟同步要差。 我们有以下问题:

1)用示波器探测,我们看到 LMK#2-5的输出在同相且频率相同(在所有芯片上)。 不过 、输入和输出会相互浮动。 这是正常的吗? 在我看来、"PLL"意味着输出针对输入进行了锁相、并且两者应该是相同的频率、或者我是不是对此存在误解?

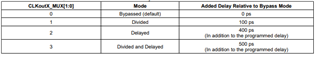

2) 2)之前的设计在第2级(LMK #2-5)使用 LMK010xx 芯片、而不是 LMK03033、并且 X 对于由不同的 LMKs 提供时钟的2个通道有一点糟糕。 这遵循 LMK03000数据表(8.9多于8个输出...)中的建议。 此处选择了 LMK03033、以便在最终时钟频率中具有更大的灵活性。 LMK03033不适用于此类2级架构、是否仅适用于 LMK010xx?

3) LMK03033和 LMK010xx 是这样的类似器件、如果2)正确、那么我想知道是否可以将 LMK03033编程为像 LMK010xx 一样工作? 例如、绕过 VCO 级、将时钟输入直接发送到输出分频器/延迟级;可能是数据表中未列出寄存器设置? (我注意到、例如、两个器件的寄存器9中的某些位设置不同、但未做说明)

注意:在这里、我们并未过度关注所有输出的相同相位对齐(根据同步功能)。 不同时钟输出的相位可以不同、只要该差异是固定的。 固定的相位偏移将在时间测量中显示为相对于零的固定偏移、并且可以进行校准。 不同的相移使精度 X 恶化