你(们)好

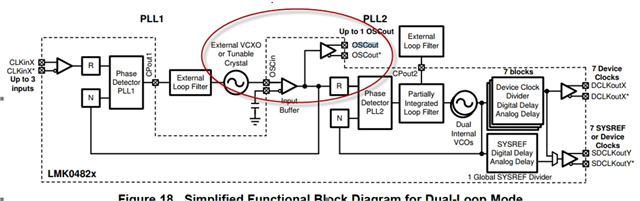

如下图所示,客户通过 PLL1评估两种 VCXO(性能更好:Crystek,性能更差:Epson )。 并使用 OSCout 作为 VCXO 的输出。

我们认为 OSCout 只是 VCXO 的缓冲输出、并叠加缓冲器本身的噪声、与 VCXO 的输出相比、OSCout 的相位将变得更糟。

但实际上我们看到:

1.无论客户使用哪种 VCXO、OSCout 都有相似的相位噪声性能

1.缓冲器 在使用 EPSON VCXO 时会优化 VCXO 输出的相位噪声,与 Crystek 相比,它的相位噪声性能更差。

我的问题是:

为什么缓冲器可以优化 VCXO 的相位噪声性能、现象的理论是什么?

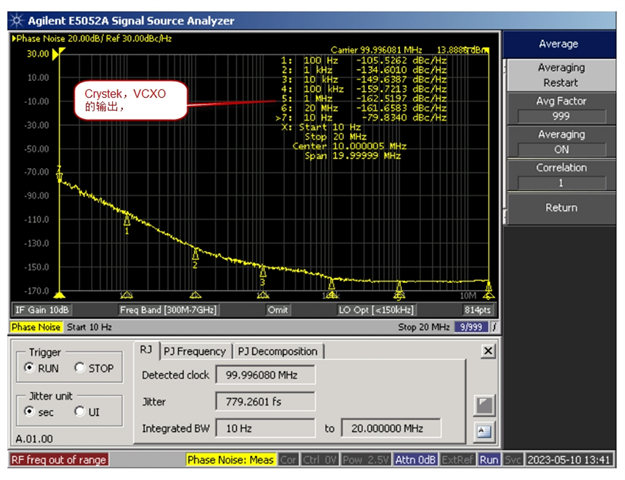

图片1:Crystek、VCXO 的输出

图2:Crystek、OSCout 输出

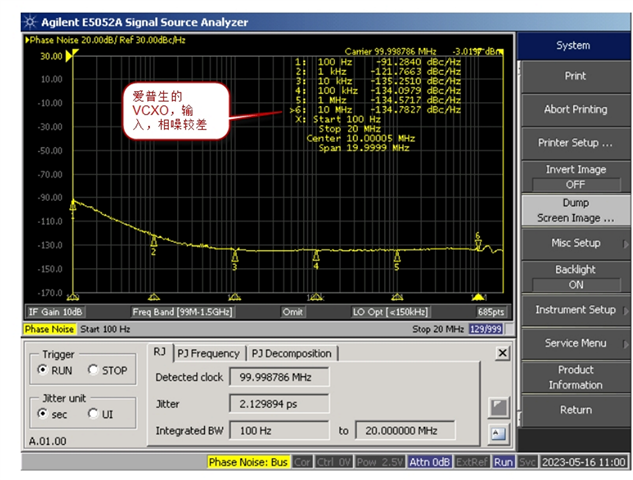

图3:Epson,VCXO‘s 输出与 Crystek 相比具有更差的相位噪声

图4:Epson,OSCout 输出,相位噪声已 优化。