请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

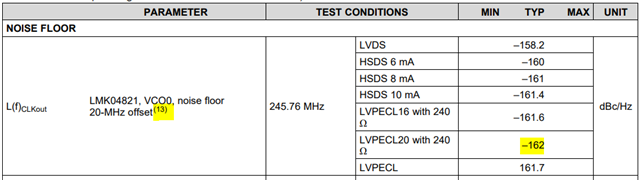

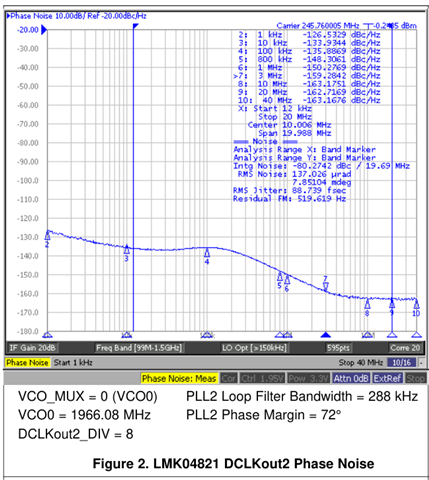

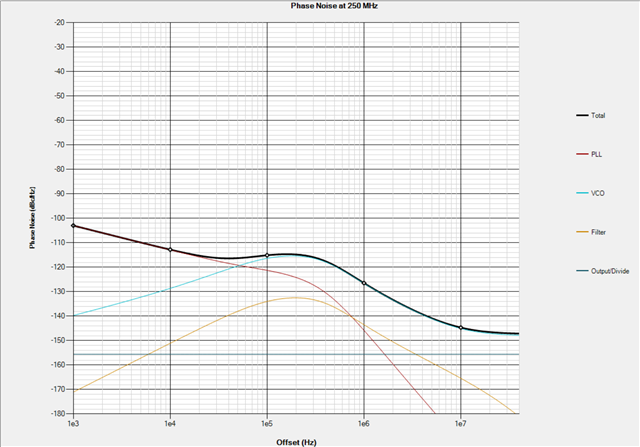

器件型号:LMK04821 LMK04821 PLLatinum Sim 相位噪声远未与数据表图接近。

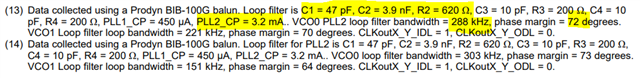

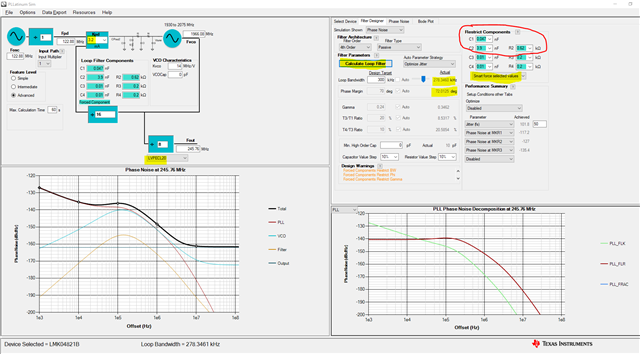

我已经尝试仿真数据表中使用的~μ s 频率计划、匹配滤波器 BW 和相位裕度。 我使用了125MHz 基准和2GHz VCO、但应该没有什么区别。 我已禁用基准噪声、并且仅将 PLL2与 VCO0一起使用。

集成相位噪声高出~10倍、主要由 PLL 噪声决定。 这是该工具提供的内置噪声曲线(PLLatinum 单选按钮中的"使用指标")。 如何使用仿真工具来适当设置 PLL 噪声、以便我在仿真中的结果与数据表中的实际结果匹配?

谢谢。

标记