请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TLC555-Q1 主题中讨论的其他器件:SN74CB3Q3245

嗨、团队,

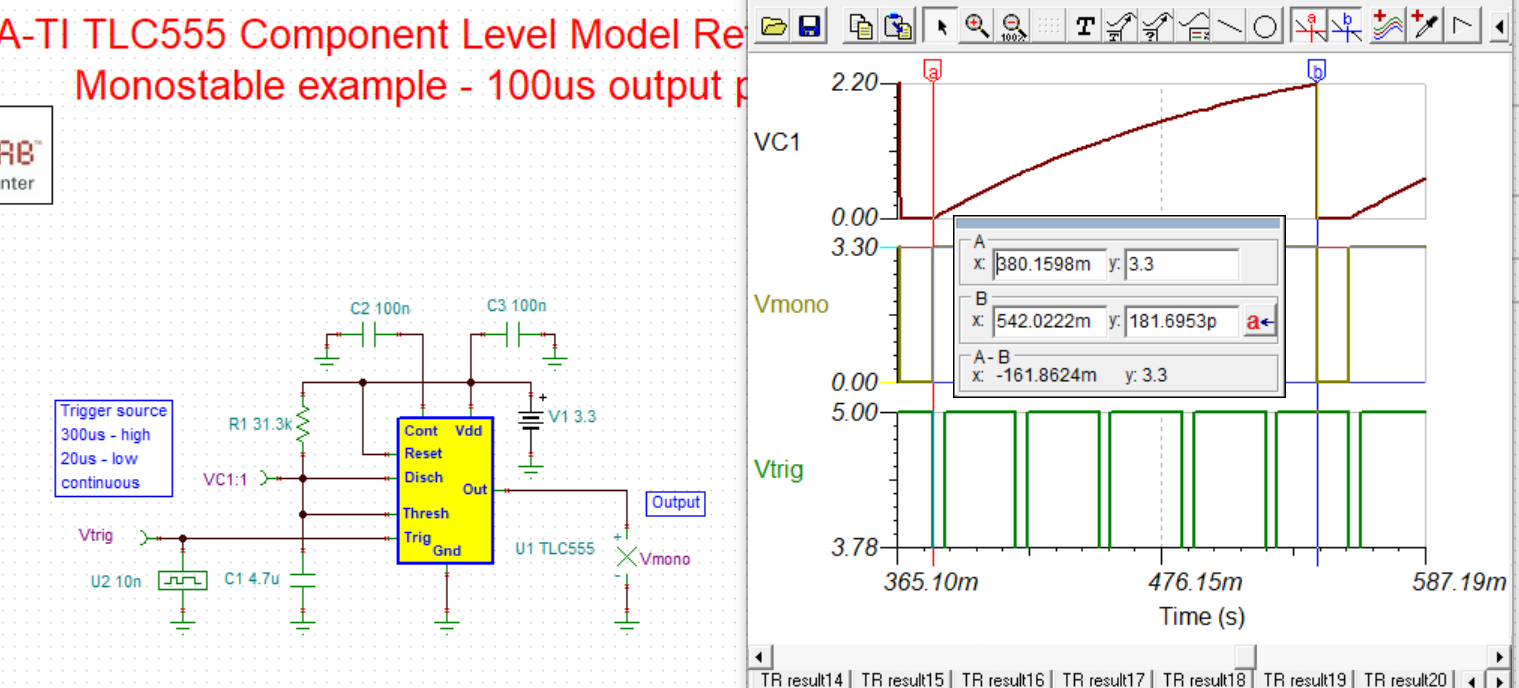

客户发现 SN74CB3Q3245的 IO 模型无法设置为输出、为什么? 您可以提供帮助吗? 输出高电平持续时间 TH: 0.939 x 49.9K x 4.7uF = 162ms。这是正确的吗?

e2e.ti.com/.../TLC555QDRQ1-schematic-review.pdf

此致、

海亮