Other Parts Discussed in Thread: LMK5C33216

大家好、

对于一个新项目、我想探索将您的 LMK5C33216器件用作无线电模块的 SYSREF 和参考时钟发生器的可能性。

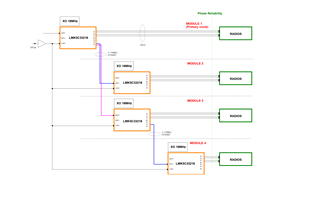

我需要在路径上连接的4个模块之间建立一个同步网络,因为之前的实施(旧背板),所以我不能建立一个星形时钟分配路径。

必须满足两个主要要求:

1)系统必须保证每次重启时的相位一致性(或者、所有输出重启时模块输出之间必须有一个已知的相位)。

我计划使用 ZDM 通过模块之间的3.84MHz SYSREF 信号实现该功能。)

使用随附图中所示的配置、您认为是否有可能获得与单个 LMK5C33216器件之间的输出偏差相当的模块之间的相位确定性?

2)主器件(模块1、系统主时钟源)必须能够通过运行在其自身的 DCO 上来调整所有系统输出(4个模块)的频率。

你认为有什么障碍吗?

Tnx