您好!

以下时钟发生器(器件型号:LMK04828BISQ)可用于某一应用、为 DUT 推导100MHz 时钟。

观察结果:

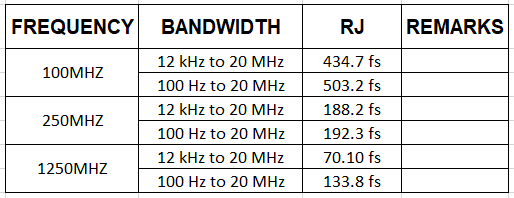

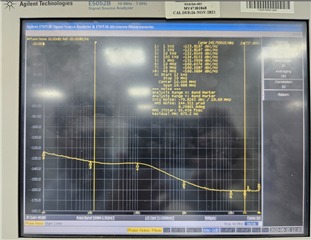

结果表明、 电路板中的随机抖动约为700fs。 但是、数据表指出"12kHz 至20MHz 时为88fs RMS 抖动、100Hz 至20MHz 时为91fs RMS 抖动。

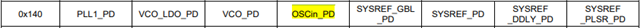

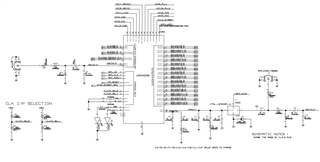

附加了原理图和寄存器设置详细信息。

请查看原理图和寄存器设置详细信息、并告诉我们您为减少设计中的抖动而提出的建议。

e2e.ti.com/.../LMK04828_5F00_REGSETTING.loge2e.ti.com/.../LMK04828_5F00_CLOCK-SECTION.pdf

谢谢!

Dhanasekaran.v