主题中讨论的其他器件:ADC32RF45、

我们正在 adc32rf45和 Stratix 10 Intel FPGA 之间尝试 JESD 接口、但我们无法在 ADC 和 FPGA 之间实现链路。

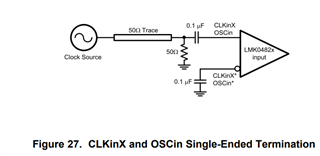

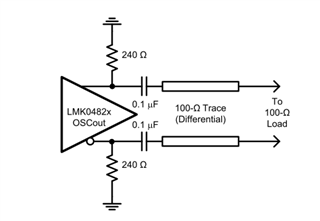

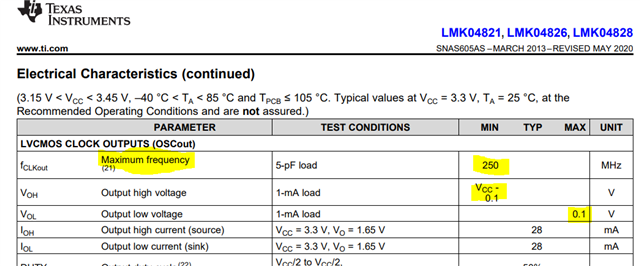

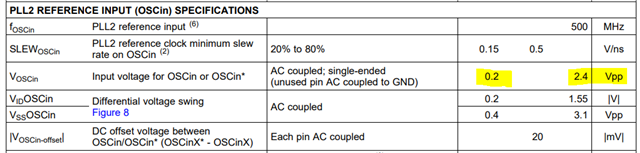

因此、我们尝试了 JESD IP 内核与回送条件、但我们无法使用 收发器时钟(lmk04828的输出时钟之一)作为输入参考时钟来获得 ATX PLL (IP 内核)锁定输出。

由于没有发生锁定、我们不确定 收发器的时钟是稳定的。

我们做了一些测试来检查时钟稳定性。

下面附上了用于检查稳定性的 LMK 配置和测试结果。

有人能告诉我们、不锁定的问题可能是什么。