您好!

我的客户对 LMK04826 SPI 接口时序有疑问。

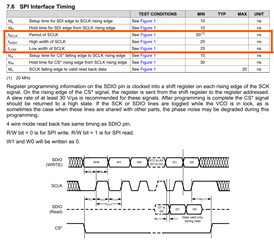

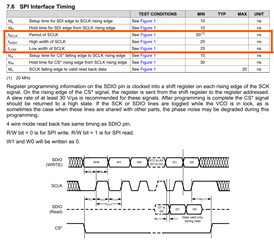

这是 LMK04826数据表中的 SPI 接口时序表

q1) SCLK 的周期规格最小为50ns (20MHz)。 当客户使用20MHz 作为 SCLK 时、他们担心裕度不足。

使用20MHz 时是否会有任何问题? 另请说明原因。

Q2 ) SCLK 的高/低宽度规格最小为25nS。 当客户使用20MHz 作为 SCLK 时、如果高:低比率不是5:5、那么一侧将小于25nS。 有问题吗?

谢谢你。

JH

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我的客户对 LMK04826 SPI 接口时序有疑问。

这是 LMK04826数据表中的 SPI 接口时序表

q1) SCLK 的周期规格最小为50ns (20MHz)。 当客户使用20MHz 作为 SCLK 时、他们担心裕度不足。

使用20MHz 时是否会有任何问题? 另请说明原因。

Q2 ) SCLK 的高/低宽度规格最小为25nS。 当客户使用20MHz 作为 SCLK 时、如果高:低比率不是5:5、那么一侧将小于25nS。 有问题吗?

谢谢你。

JH

JH:

1) 20MHz 没有问题。 每个器件都使用>20MHz 的 SPI 总线进行了生产测试、特性化可保证 SPI 接口上有足够的时序裕度(几乎快一个数量级)。 我认为这只是 TI 制定的一个奇怪的规范、因为 我们并没有清晰地概括"高宽"和"低宽"的含义。 该图表明、这两种标准分别适用于高于 VCC 50%和低于 VCC 50%的情况、但这可能不是最好的衡量标准。 可以说、"高宽度"从 VIH 的正阈值交叉点延伸到 VIL 的负阈值交叉点、"低宽度"从 VIL 的负阈值交叉点延伸到 VIH 的正阈值交叉点。

在任何情况下、我想我们都试图传达这样的情况:占空比大约为50%的20MHz 时钟是可以的、或者具有25%占空比的10MHz 时钟是可以的、等等。

2) 2)请注意、数据设置和保持时间列示为每个最小10ns。 以此为指导、我想说、20MHz 时、SCLK 可接受50±10%的占空比、占空比误差是压摆率限制或某个可变脉冲宽度的函数。 除了最小高宽和低宽度、低于20MHz 时没有明显的占空比限制。

请告知客户、我们已在远高于20MHz 的频率下通过 PVT 测试此总线、但没有问题、因此50%占空比的微小变化或上升/下降时间容差不会是问题。 THIGH = 20ns 或 TLOW = 20ns 不会阻止 SPI 通信。

此致、

D·佩恩