主题中讨论的其他器件: ADC32J25

您好!

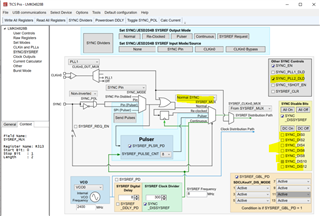

通过附加的 TICS Pro 配置、SDCLKout1没有 SYSREF 输出。

此外、还附上了原理图副本。 LMK04828电路位于表18中。

我是需要使用脉冲驱动 SYNC 引脚(引脚6)还是将其设置为高电平?

此致、

安德鲁

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

通过附加的 TICS Pro 配置、SDCLKout1没有 SYSREF 输出。

此外、还附上了原理图副本。 LMK04828电路位于表18中。

我是需要使用脉冲驱动 SYNC 引脚(引脚6)还是将其设置为高电平?

此致、

安德鲁

您好、Vicente:

e2e.ti.com/.../HexRegisterValues_5F00_072023a.txt

从0x0000到0x1FFF 写入后、我在137和147行中完成了 SYSREF 设置过程。

0x013900

0x014319

0x01000F

0x01080F

0x013A01

0x013B2C

0x014008

0x014319

0x013E03

0x014339

0x014319

我可能没有重写每个建议的寄存器、但我认为我解决了所有关键步骤。

我似乎仍然看不到 SDCLKout1的 SYSREF 输出。

您能看一下寄存器吗?

谢谢!

安德鲁

您好、Vicente:

这是生成了导出寄存器的 TICS pro 文件。

在 TICS Pro 中、VCO0为2400 MHz。

我还将重试 SYSREF 生成。

谢谢!

安德鲁

Andrew、您好!

在收到上述配置文件(LMK04828b_v072123a.TCS)的情况下、器件处于同步模式(SYSREF 输出关闭)、一旦 PLL2锁定、所有 DCLK 分频器都将复位。

若要在连续模式下生成 SYSREF、请在 PLL2锁定后执行以下写入。

1.0x144 --> FF

2. 0x143 --> 11

3. 0x139 -> 03

谢谢!

此致、

阿杰特·帕尔

尊敬的 Ajeet:

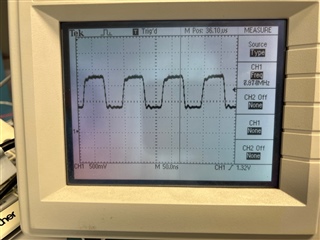

8 MHz Sysref 在遵循您的建议后工作!

下面还附加了.TCS (与您的相同)和我使用的.hex 文件(基本上从 TICS Pro 导出、并在0x1FFF53之后添加了您建议的命令

e2e.ti.com/.../LMK04828_5F00_JESD204B_5F00_Config_5F00_Cust.tcs

e2e.ti.com/.../HexRegisterValues_5F00_072423c_5F00_ti.txt

非常感谢

安德鲁

附注:我想再留几天、因为我现在也要让 ADC 正常工作。

此致、

安德鲁

尊敬的 Ajeet:

您能否查看原理图? 我也对与时钟相关的电路做了笔记。

再次感谢、

安德鲁

Andrew、您好!

您能够获得 SYSREF 输出。

关于您的原理图、请查看以下备注:

[/报价]

- DCLKOUT2p/n (ADCCLKP/N):在幻灯片5上、我认为 ADC32J25需要 LVDS。 那么、我应该按照幻灯片2中所述更新电阻器吗?

- SDCLKOUT3p/n (SYSREFP/N):此处存在相同的问题。 我是否应该更新电阻器?

从 ADC 数据表中、以下是 LVDS 和 LVPECL 输入时钟的预期电路。

您的电路板原理图显示了 LVPECL 输入格式的终止。 因此、您可以保持 R412、R415、R418和 R419的原样、并使 LMK04828 DCLKout2和 SDCLKout3输出设置为 LVPECL 格式。

[/quote][/报价]

- DCLKOUT8p/n (PCIe_CLK1P/N):用于 PCIe。 请告诉我、这看起来是否合适、

- SDCLKOUT9p/n (PCIe_CLK1P/N):用于 PCIe。 请告诉我、这看起来是否合适、

按照 LMK04828数据表的第10.4.2节、如果接收器没有内部端接、则可以保持 DCLKoutx_P 和 DCLKoutx_N 之间 的100ohm 电阻。 则保持560 Ω 的电阻通过它们。

基于 PCIe 接收器终端、您可以遵循 上述建议。

谢谢!

此致、

阿杰特·帕尔