您好!

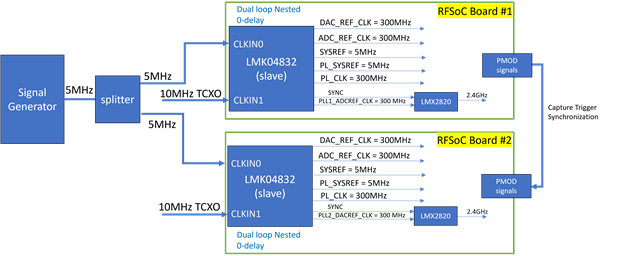

我当前正在使用以下设置来实现多板多逻辑块同步。

我正在使用分离器将5MHz 信号馈送到两个 RFSoC 板中、如下所示。 我已经使用了 LMK04832的寄存器并将其编程到两个 RFSoC 板上、但无法使多板时钟同步。 附件是 TCS 文件和寄存器。

1) 1) 检查了 Status_LD1引脚、似乎 PLL1未锁定。 为什么?

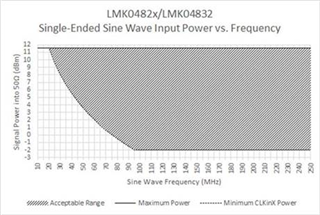

2)我们设置了哪些配置来确保 LMK04832只使用外部时钟来实现 Mb MTS ? 外部时钟5MHz 将馈送到 LMK04832从板的 CLKIN0。

e2e.ti.com/.../LMK04832_5F00_SYSREF_5F00_ZDM.tcse2e.ti.com/.../LMK04832_5F00_SYSREF_5F00_ZDM_5F00_hexregisters.txt