您好!

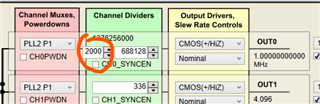

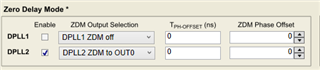

当在输入端配置1PPS 基准以及在输出端配置1PPS、16kHz 和4.096MHz 时、LMK05028EVM 存在问题。 时钟输出需要与输出1PPS 时钟进行相位对齐。 正如其他人在此论坛上指出的那样、我难以验证1PPS 基准信号。 我也无法使用有效的1PPS 输入使 DPLL 锁定。

我已经尝试用一个任意函数发生器和一个 Furuno GT-8801精密振荡器来生成1PPS 参考。 我们产品的实际1PPS 时钟源将是 Quectel L26T-S89,但这还没有经过测试。 启用1PPS 抖动阈值监视器(处于最大值)时、两个测试源都存在基准验证问题。 我有时可以使用任意函数发生器使1PPS 进行验证、但它对电压等看起来非常敏感。

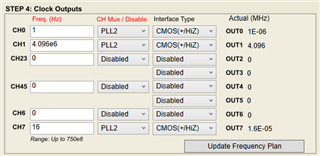

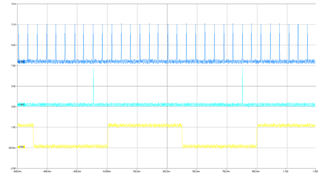

除了难以获得基准进行验证外、我还无法让 DPLL 锁定在此配置中。 我尝试了在此论坛中针对此器件提出的建议、但在成功进行基准验证后、无法获得频率和相位锁定信息。 以下是输入1PPS 信号(黄色)、输出1PPS 信号(青色)和输出16Hz 信号(蓝色)的波形。 对于低于大约1200Hz 的输出频率、输出未被锁定并且在50%的占空比下。

使用"Run Script"中的设置的 TICS Pro 文件为: e2e.ti.com/.../MDAQ_5F00_LMK05028_5F00_1PPS_5F00_LO_5F00_16HZ.tcs

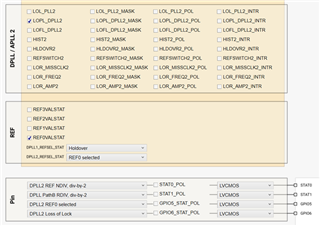

基准输入监视器设置如下所示:

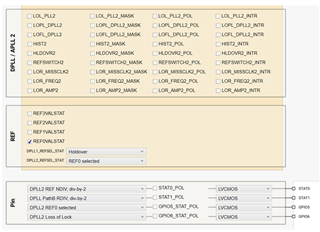

DPLL 锁定检测器的配置如下:

谢谢。