Other Parts Discussed in Thread: LMK5B33216EVM

您好!

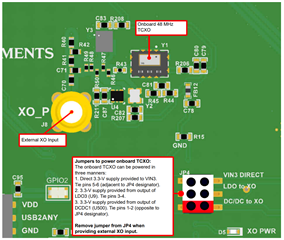

我们将尝试分析 LMK5B33216EVM 板的相位噪声。 我们将使用 SIT5347AE-FN-33E0B100.000000 MEMS 振荡器、生成一个100MHz 信号、该信号连接到评估板上的 Y3蓝图:

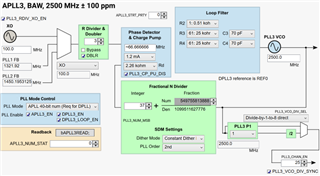

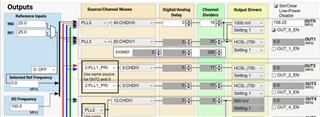

我们将仅使用 APLL3 (禁用 DPLL)生成156.25 MHz 输出、并在 TICS PRO 中使用这些设置:

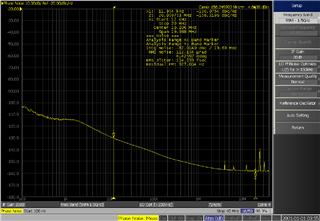

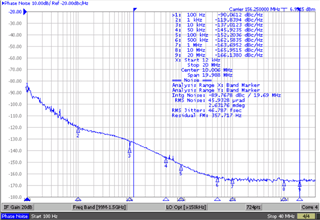

不过、 在使用我们的 E5052B 信号源分析器测量相位噪声时、与数据表相比、我们会观察到比预期更大的 RMS 抖动(较高频率下存在明显的杂散、远远超出环路滤波器带宽):

您能告诉我们、问题的根源是什么、尤其是高频杂散吗? 提前感谢您!

此致!

乔尔