请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK00301 您好!

我正在使用 LMK00301A 的125MHz 的3.3V LVDS 输出。 该输出作为以太网 QSGMII PHY 88E1552的 REFCLKP/N 输入的输入。

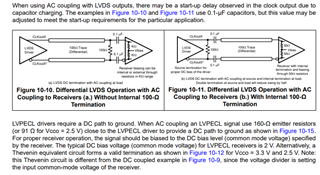

我使用0.01uF 电容器作为交流耦合电容器、接收器处有一个100欧姆的差动终端。

附加了信号完整性模拟快照。 将3.3V LVDS 输出连接至1.8V LVDS 额定输入时、建议的端接方案是什么?

谢谢。