主题中讨论的其他器件:CDCLVP111

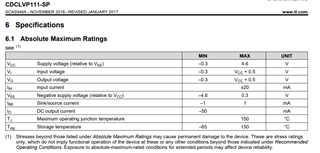

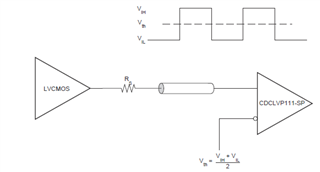

对于以前关于单端输入的问题、我们的回答还不够充分。 一个桥臂的最大 VID 是1.3V 是真的吗、这样该器件将被如图所示连接的3.3V 单端输入损坏。 8? 或者、由于该器件未经单端输入测试、且该设计能够承受更大的摆幅、这只是特性限制吗?

如果确实存在损坏风险、数据表图8 (如下所示)会具有很大的误导性。 它仅适用于1.2V LVCMOS 输出、这在振荡器中很少见。 但我怀疑1.3V 是否真正阈值、在该阈值下、器件将开始出现问题。

另一个问题:在数据表中、CLKn 的 VCM 最小值为1V。 另一个问题/回答指出、单端输入必须满足这一要求。 如果需要分压、这似乎与上面的图完全相矛盾。 为了说明明显性、将 LVCMOS 信号分压到1.3V 将具有0.65V 的 VCM、这小于1V。 调节这将需要增加交流耦合+直流偏置。 请解释这些不一致之处。