大家好、

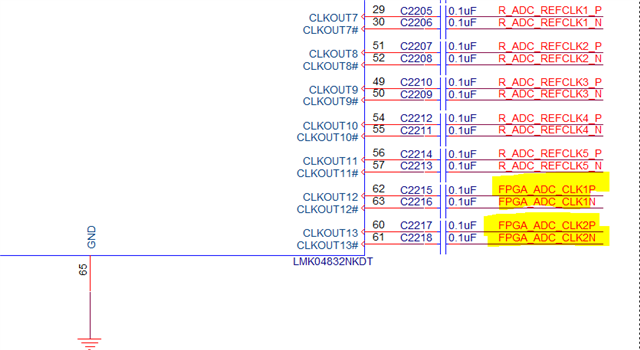

我们正在 我们的一个项目中使用 LMK04832NKDT。 请建议我们是否可以继续使用以下 LVDS 时钟输出端接方法和值。

(100E 的分裂终端在目标端此处使用)。

(100E 的分裂终端在目标端此处使用)。

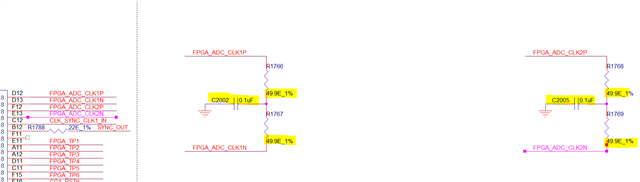

参考 EVB 时、我们发现电容器位于端接电阻器之后。

请建议我们是否可将交流耦合电容器放置在 IC 本身附近并在目标附近放置端接(分裂或单个100E)。

或者应该遵循 EVB 方法首先端接、然后是交流耦合电容器(都在目标端)?

另请注意、对于我们而言、源 IC (LMK)和目标 IC (FPGA)位于不同的卡上。