Other Parts Discussed in Thread: LMK04832

主题中讨论的其他器件:LMK04832

您好!

为了了解 LMK04832的工作原理、我们提供了 TI 提供的评估卡。 (VCXO 122.88 MHz)

我想在"保持"模式下使用 LMK04832、我想获取有关退出该模式的更多说明。

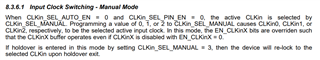

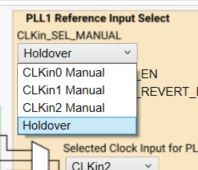

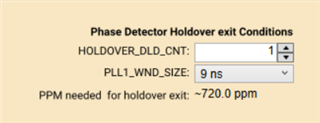

在"pll1 holdover control"上、我选择退出模式"exit based on DLD"

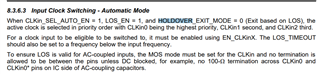

我使用连接到 CLKin1的外部10MHz 参考时钟。 (未选择 CLKin0)

该参考时钟可能存在、也可能不存在。

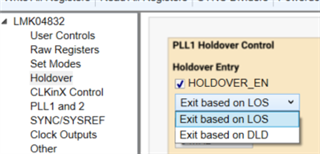

当该时钟不存在(10MHz 参考时钟= OFF)时、LMK04832会使用预先建立的 DAC 电压(CPout1)切换到"保持"模式。

另一方面、当返回该参考时钟时、LMK04832保持在"保持"模式、它不想锁定到此参考时钟。

你能向我解释一下吗?

第二种情况、我们可以根据外部时钟的频率来调整进入"保持"模式吗。

我通过改变外部参考时钟10MHz PLL1+350Hz 和 PLL1-520Hz 的频率来观察运行情况 PLL1关闭(10MHz 关闭)

VCXO 上的电压随外部时钟频率的变化而变化(VCXO 上的电压是0或+3.3V)。

另一方面、当 PLL1关闭时、我希望 LMK04832能够切换到"保持"模式。

有可能吗?

附件为 Holdover_mode_exit_based_on_DLD.tcs 文件

e2e.ti.com/.../Holdover_5F00_mode_5F00_exit_5F00_based_5F00_on_5F00_DLD.tcs

感谢您提供的帮助。

此致

大卫