您好!

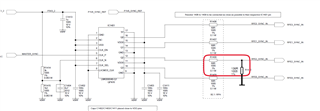

我的电路设计如下供大家参考、现在 VDDO 是1v8、Q2通过两个电阻分压连接到 FPGA I/O (因为 FPGA I/O 输入电压范围是1V-1.8V)、我想把 FPGA 输入电压保持在1.2V 左右。

我的问题是、我是否可以以这种方式使用 Q2输出?

如果否,请说明理由和其他建议。

如果是、案例的当前状态是什么? Q2电流驱动器功能足够或不?请帮助计算值,我在数据表中找不到输出电流参数。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我的电路设计如下供大家参考、现在 VDDO 是1v8、Q2通过两个电阻分压连接到 FPGA I/O (因为 FPGA I/O 输入电压范围是1V-1.8V)、我想把 FPGA 输入电压保持在1.2V 左右。

我的问题是、我是否可以以这种方式使用 Q2输出?

如果否,请说明理由和其他建议。

如果是、案例的当前状态是什么? Q2电流驱动器功能足够或不?请帮助计算值,我在数据表中找不到输出电流参数。

尊敬的 Wu:

您可以使用分压器达到输出端所需的 VOH 电平。 考虑到缓冲器的7欧姆输出阻抗、可以将 R1410降低到150以获得更接近1.2V 的值。

流经驱动器并到达输出端的电流计算 公式如下:

输出电流 = VDD /总阻抗= 1.8/(7+ 68 + 150)= 8 mA

一个线性调频脉冲。

输出电流 = VDD /总阻抗= 1.8/(7+ 68 + 150)= 7.4 mA

此致!

阿西姆