您好!

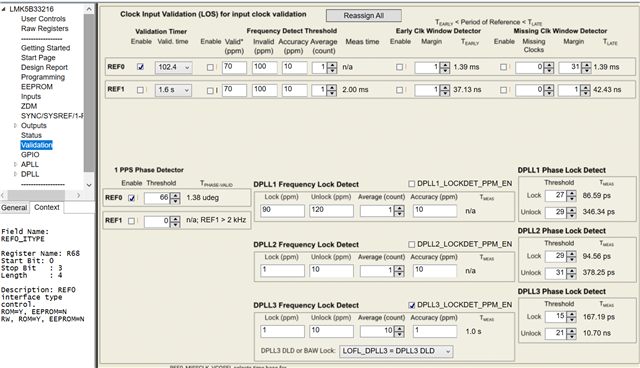

我曾尝试使用1pps 锁定 DPLL3、使用48MHz 的 TCXO 锁定 APLL3、以在输出端口4处实现156.25MHz 的输出。 我使用的 PDF 是32MHz。 我无法 使用48 MHz TCXO 使 LMK5B33216的锁相一致达到1pps。 有一段时间它会锁定、但这是间歇性的、不会保持锁定状态、即使在等待了长达60分钟之后也是如此。 几周前、我得到了100MHz TCXO 案例(包含66.6666MHz 的 PDF)的支持、该案例会 在10分钟后产生锁相、但在48 MHz 下运行时至少需要20分钟才能锁定。 除了缩短锁定时间、有什么设置可以实现吗? 仅供参考、这是我使用的验证页面。 验证 DPLL3锁相检测似乎未 保存我在召回时输入的新数字。 每当我调用状态文件时、我都必须重新输入新值。 你有什么想法吗?

我观察锁定状态的方式是监视板上的三个 LED。 请参阅所附图片、红色矩形区域。 通过 在 GUI 上将 GPIO1设置为 LOPL_DPLL3、我相信一旦 DPLL3锁定、中间的 LED 就会关闭。 在锁定过程中、中间 LED 常亮、而左右 LED 交替闪烁。 一旦锁定、中间 LED 指示灯熄灭。 我认为这意味着它被锁定了。 大约30-45分钟后、我发现中间 LED 再次亮起、左右 LED 同时闪烁。 我认为它失去了锁定状态。 如果有任何东西缺失、请告诉我、或尝试一些方法。

如果您能够以可靠、快速的方式为使用48MHz TCXO 的1pps 锁的用例提供状态文件、那将非常棒。

谢谢。