主题中讨论的其他器件: LMK04832

大家好、

客户正在尝试验证 lmk04828的数字和模拟延迟。

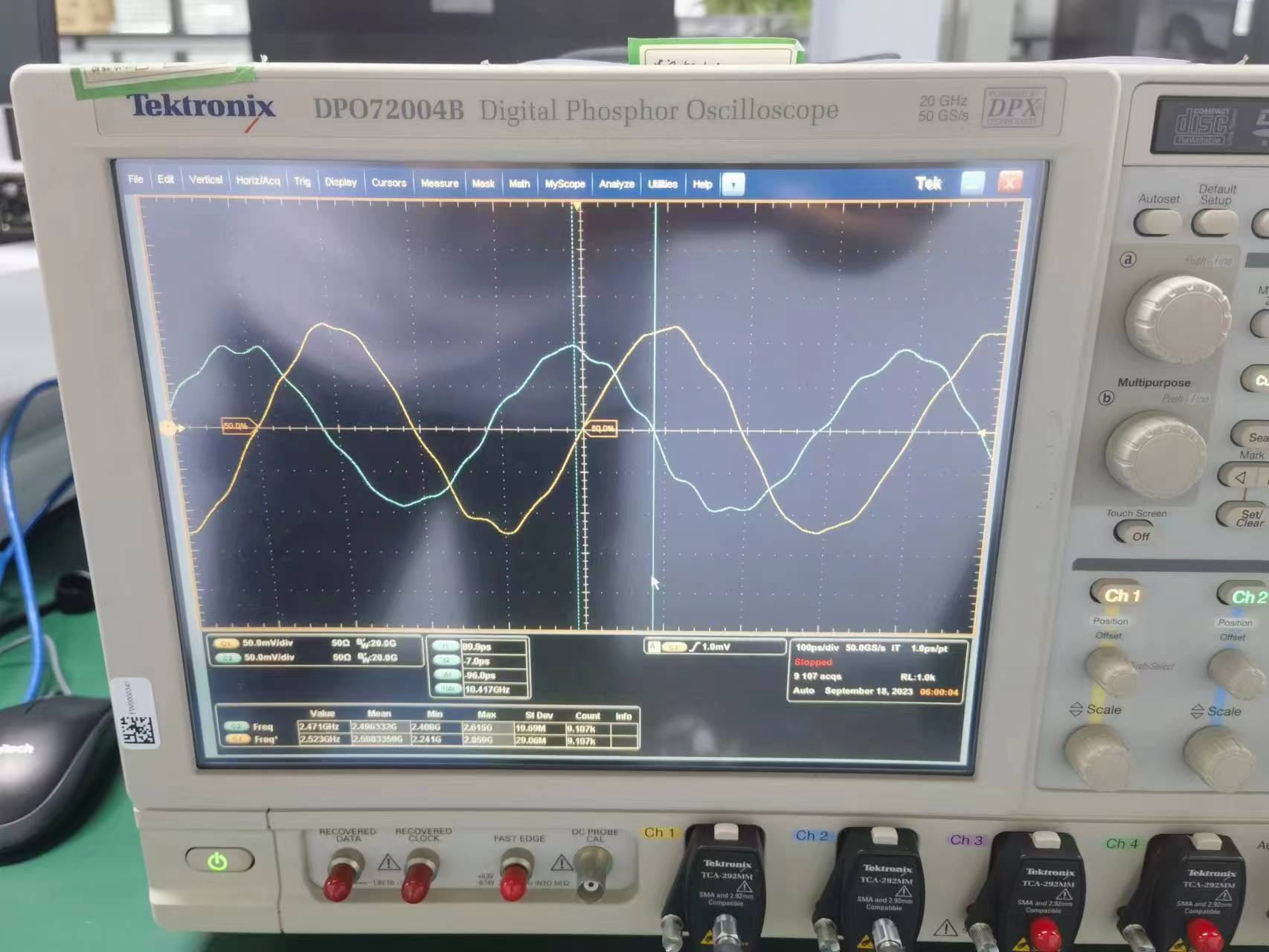

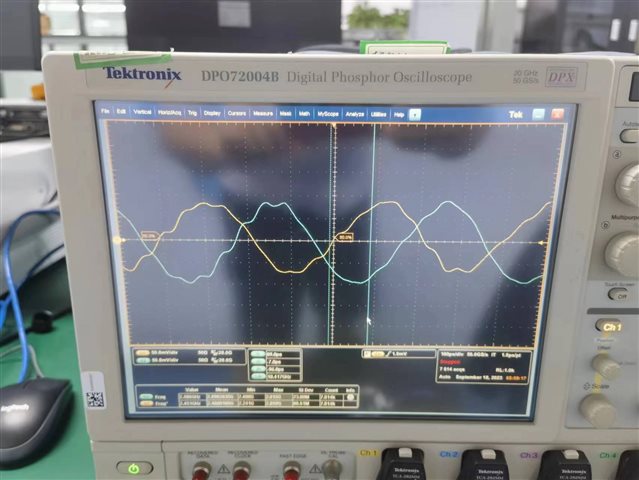

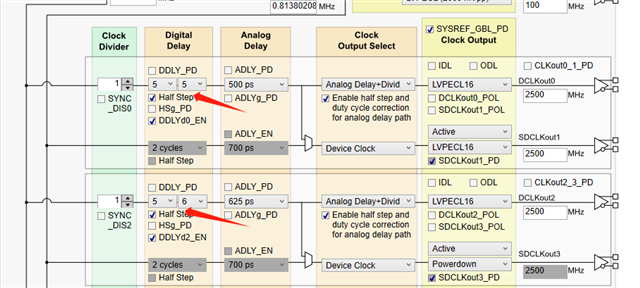

clkin1输入是20 MHz 时钟、而 oscin 输入是100 MHz 时钟。 Vco0为2500 MHz。 Dclkout0为2500 MHz、dclkout2为2500 MHz。 使用示波器测试这两个时钟的延迟。

关于模拟延迟:将时钟输出选择设置为 TICSPRO 上的模拟延迟+分频器。 芯片配置完成后、更改模拟延迟中的延迟值、以查看时钟延迟确实发生了变化、但更改后的值和设定值不同。

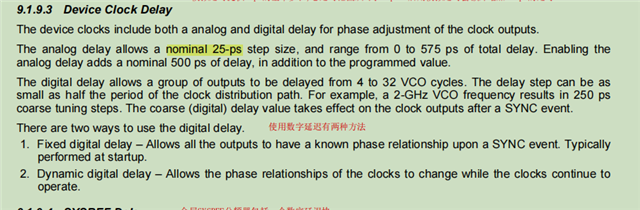

关于数字延迟功能、根据手册有两种模式:

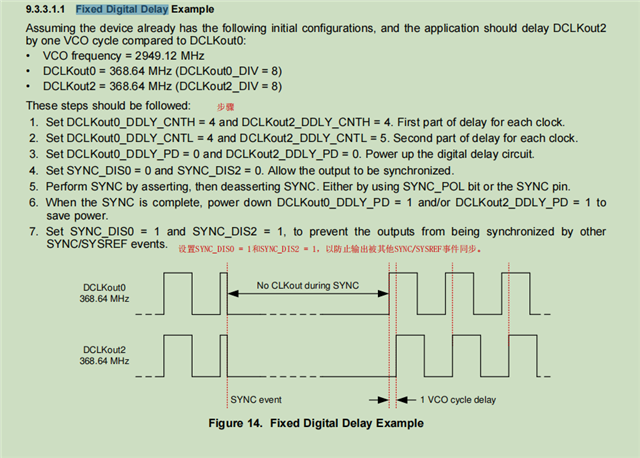

客户尝试使用手册上的示例验证固定数字延迟:

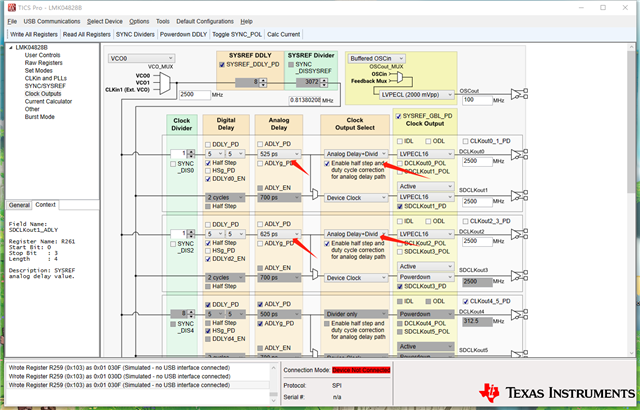

- 将 DCLKout0_DDLY_CNTH/L 设置为值4、4;

- 将 DCLKout0_DDLY_CNTH/L 设置为值4、5;

- 设置 DCLKout0_DDLY_PD = 0且 DCLKout2_DDLY_PD = 0;

- 设置 SYNC_DIS0 = 0且 SYNC_DIS2 = 0;

- 然后、SYNC_POL 依次写入1和0。

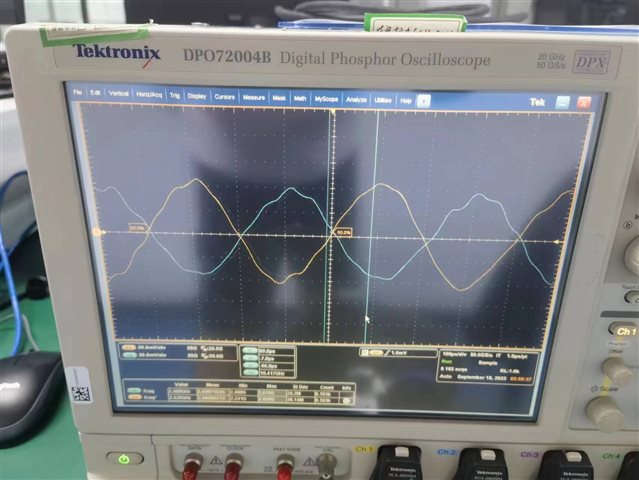

已知 VCO0为2500 MHz。 修改后的延迟为半个 VCO0周期、即它应为200ps、这意味着应将 dclkout0和 dclkout1反相。 但输出时钟实际上并不会改变。

您能帮助了解这种情况吗? 谢谢。

此致、

切里