主题中讨论的其他器件: LMK04828

您好!

我正在使用 TICSPRO-SW 将 PLL 电路设置为"LMK04828B"。

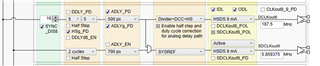

我想知道两个特定输出信号"CLKout8_9_PD"和"SDCLKout9"之间的相位延迟。

是否可以根据设置的参数估算延迟?

根据我的设置显示 LMK04828B 的时序图也没有问题。

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我正在使用 TICSPRO-SW 将 PLL 电路设置为"LMK04828B"。

我想知道两个特定输出信号"CLKout8_9_PD"和"SDCLKout9"之间的相位延迟。

是否可以根据设置的参数估算延迟?

根据我的设置显示 LMK04828B 的时序图也没有问题。

此致、

高田山市

虽然我们很长时间以来都希望根据延迟设置在 GUI 中提供一个时序图、但很遗憾、我们没有时间创建此工具。

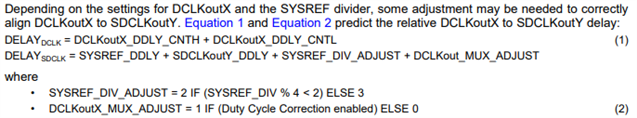

您可以使用 LMK04828数据表第9.3.4节中提供的公式计算以 VCO 周期为单位的估算延迟。

我刚刚注意到这个公式中的一个错误: 应将 DCLKout_MUX_ADJUST 添加到 DELAYDCLK、而不是 DELAYSDCLK 。

那么、让我们完成您的示例:

从您的屏幕截图中可以看出 SYSREF_DDLY 不明显、但假设它是8个周期。 在这种情况下、DELAYDCLK = 11个周期、而 DELAYSDCLK = 12个周期、因此 SYSREF 延迟将使 DCLK 延迟滞后一个 VCO 周期(一个3000 MHz VCO 周期、或333ps)。

如果 SYSREF_DDLY 设置为15、则 DELAYDCLK = 11个周期且 DELAYSDCLK = 19个周期、因此 SYSREF 延迟将使 DCLK 延迟8个 VCO 周期。 由于器件时钟为每周期16个 VCO 周期、 如果 SDCLK 将 DCLK 滞后8个周期、则 SDCLK 上升沿与 DCLK 下降沿同时发生。

最后、有四个条件未被公式考虑:

——

请注意、Connor 之前的指导不正确-仅 动态数字延迟需要 DDLYd8_EN、该功能允许在同步后更改延迟。 如果您同步输出、 上面公式中的固定延迟值仍将在清除 SYNC_DISx 的任何通道上生效。 LMK04828数据表的第9.3.3节 详细介绍了固定数字延迟和动态数字延迟的步骤及其之间的差异。

此致、

D·佩恩