请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMX2541 大家好、

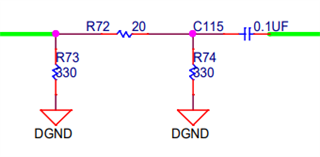

我是 FAE Jayden、我的客户在其系统中使用 LMX2541SQE30E/NOPB。 客户发现 FPGA 配置的1GHz 正弦时钟信号输出的上升沿/下降沿不是理想的(请参阅测试波形)、需要帮助排除该问题。

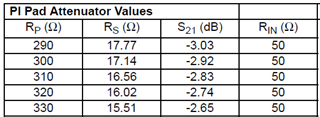

原理图和测试波形如下:

1.要获得更理想的正弦时钟信号输出、是否可以通过 SPI 配置参数对其进行改进? 或者、 PCB 等硬件是否有改进? 是否有任何特定 SPI 配置的相关信息可提供给客户的 FPGA 工程师以供参考?

2.对于时钟信号的相位噪声指标测试、我们能提供相关的测试指导吗?

期待您的回复! 谢谢。

杰登