主题中讨论的其他器件: LMK61E2、LMK61E0M 、 LMK6C

您好!

我希望你们做得好。

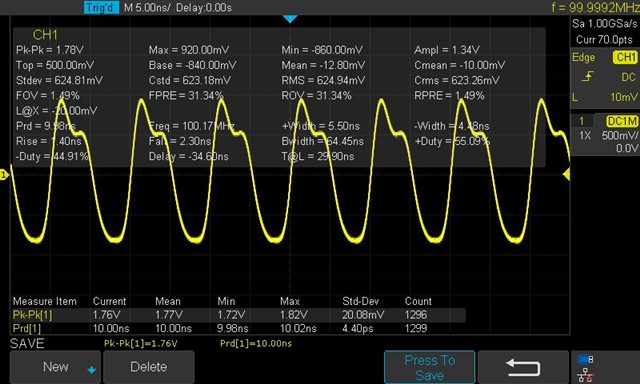

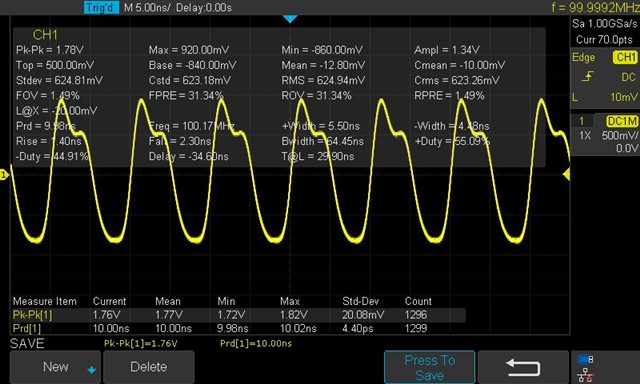

我在使用模块 LMK61E2-100M00EVM 时遇到问题。

我想了解输出时钟的问题是什么?

通常、它应该是 LVPECL 格式、但不是、并且形状也不好。

提前感谢您的回复。

此致。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我希望你们做得好。

我在使用模块 LMK61E2-100M00EVM 时遇到问题。

我想了解输出时钟的问题是什么?

通常、它应该是 LVPECL 格式、但不是、并且形状也不好。

提前感谢您的回复。

此致。

尊敬的 Thanh:

为了帮助您、您能否确认有关测试设置的一些详细信息:

1.是否使用 EVM 上的默认 LVPECL 终端方案?

2. 此测量是使用高阻抗探头进行的还是示波器上的50欧姆终端? 与数据表中指定的值相比、额外的50欧姆端接可实现不同的振幅测量值

3. OUTP 和 OUTN 是否都连接到示波器? 如果由于 LMK61E2输出驱动器上的负载不匹配而仅连接其中一个、则信号完整性可能会更差。

此致、

康纳

尊敬的 Connor:

1.是

2.用同轴电缆连接模块和示波器

3、我只把 OUTN 连接到示波器

实际上、我使用此时钟激活 ADC DC782A-T www.analogue.com/.../dc782a-t.html。

但是、ADC 输出端有很多噪声。

如何解决该问题?

提前感谢您提供建议。

此致。

尊敬的 Thanh:

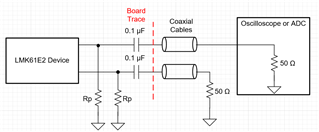

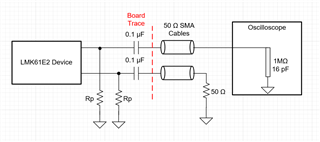

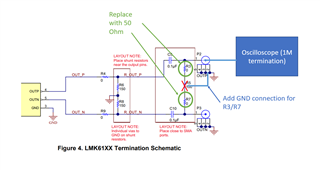

由于 ADC 只有1个端接电阻为50欧姆的时钟输入、因此我建议通过50欧姆负载端接 LMK61E2的未使用输出、以便 OUTP 和 OUTN 都具有相同的端接。 下面是一个简单的原理图示例:

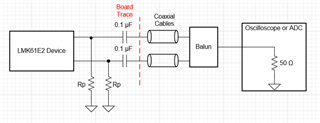

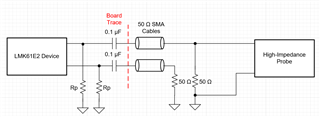

请注意、Rp 和0.1uF 电容器应已组装在 EVM 上。 另一种选择是使用平衡-非平衡变压器将差分信号转换为单端信号、并像这样将其直接连接到示波器或 ADC:

请告诉我这是否有助于改善示波器上的波形或 ADC 的噪声。

此致、

康纳

尊敬的 Thanh:

抱歉延迟了响应、我 在实验室尝试了 LMK61E2 EVM (具有默认的交流耦合 LVPECL 终端)、我看到了约900mV 的单端摆幅、并且没有过冲问题。 这是在具有内部50欧姆端接的示波器上测得的。 您能否确认示波器是否具有内部50欧姆端接或是否设置为高阻抗? 另外、这些测量是在启动时进行的还是稳态行为?

我已经联系了我团队的其他一些成员来讨论 ADC 上的噪声、我应该能够在第二天或第二天向您提供一些有关这方面的反馈。

此致、

康纳

尊敬的 Thanh:

抱歉混淆了、只是为了确认当您看到第一篇文章中的波形时、您是如何在示波器上测量时钟信号的?

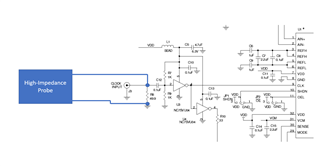

如果是、这将解释信号不匹配常规 LVPECL 电平的原因。 要了解 LMK61E2的时钟输出在 系统中的实际情况、最好的方法是使用 50欧姆负载测量信号。 该操作通常通过示波器上的内部端接来完成、但由于示波器有一个1M 端接、因此可以使用高 阻抗探头在连接 GND 的50欧姆电阻器上进行测量、如 ADC 板上的 R8电阻器。

如果您没有高阻抗探头或无法 与 R8周围的探头良好接触、 另一个选择是在 LMK61E2 EVM 上添加一个50欧姆至 GND 电阻器、并使用您之前使用的示波器上的同轴电缆至1M 端接的相同设置

这些设置中的任何一种都应显示具有适当 LVPECL 电平的干净时钟信号。 请告诉我这是否合理。

另外、根据团队其他一些成员的反馈、他们认为 ADC 上的噪声问题更有可能来自模拟输入或 ADC 配置的其他一些问题。 如果您尚未仔细检查器件的其余设置、也可以联系 Analog Devices。

此致、

康纳

尊敬的 Thanh:

理解、在这种情况下、最好使用高阻抗探头在 ADC 板上的 R8两端进行探测、以确保时钟信号符合预期。

我仔细查看了 ADC 用户指南、看起来他们建议时钟使用大振幅信号(为50欧姆负载提供2.5V 方波):

该时钟还用作 NC7SVU04缓冲器的输入、该缓冲器要求输入为0.8 * VCC、才能满足 VIH 要求。 R7和 R9将直流偏置设置为0.5 * VCC、因此、假设 VCC = 3V、信号摆幅需要至少具有1.8V 的峰峰值。 有可能切换到 LVCMOS 振荡器吗? 如果移除 R8、LMK61E0M 或 LMK6C 可以满足摆幅要求。 您还可以尝试使用平衡-非平衡变压器来转换 LMK61E2单端的 LVPECL 输出并将振幅加倍、与 LVCMOS 振荡器相比、这很可能会提供更好的抖动性能。

此致、

康纳

尊敬的 Thanh:

我们使用的一些平衡-非平衡变压器是 Minicircuits 的 ZFSCJ-2-1+和 ZFSCJ-2-4+。 如果摆幅仍然不够大、我建议使用 LVCMOS 振荡器并移除 ADC EVM 上的偏置网络、以便时钟直接进入 NC7SVU04缓冲器。 您应该能够使用2.5V 或3.3V LVCMOS 信号驱动它。

此外、在最终设计中 、您应该能够使用 LVCMOS 振荡器直接驱动 ADC 的 CLK 输入、而无需任何额外的方波转换电路。 我认为 ADC EVM 是这样设计的、因为 它假定您将使用信号发生器的正弦波来提供 CLK 输入、但是如果您使用的是 LVCMOS 时钟源、我认为没有必要这样做。

此致、

康纳

尊敬的 Connor:

您是指 LMK61E0M 和 LMK6C?

我使用过此 CMOS 时钟 https://www.mikroe.com/clock-gen-click 、但它仍然有一些类似的错误。

通常、我是否需要同步 DAQ 和 ADC 之间的时钟?

谢谢你。

此致。

尊敬的 Thanh:

没错、LMK61E0M 或 LMK6C 是我们可用于 LVCMOS 振荡器的出色器件。 LMK6C 是一款固定频率器件、因此用于设计将更轻松且成本更低。 LMK61E0M 需要编程、因此它稍微复杂一些、但在选择输出频率时可提供更大的灵活性。

我不确定您是否需要同步 DAQ 和 ADC 之间的时钟、您可能需要联系 Analog Devices。

此致、

康纳