请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK04832 大家好、

我是否可以知道如何启用 LMK04832一次性 sysref 模式? 谢谢。

B.R.

卢卡斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

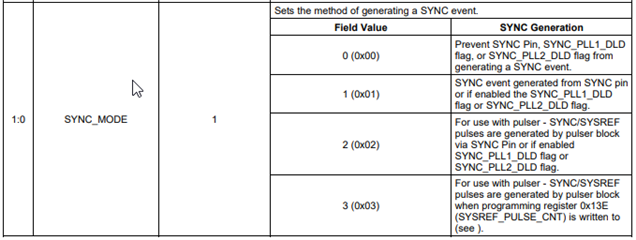

我注意到标题询问了脉冲 SYSREF 模式、但所问的问题是一次性 SYSREF 模式-这是两种不同的 情况、我想确保我们能够解答您在任一种情况下的问题:

对于 SYSREF 脉冲发生器模式、脉冲 仅是 SYSREF 分频器的选通副本。 因此、相对于器件时钟的脉冲持续时间和相位校准将与连续 SYSREF 相同。 例如、如果 SYSREF 分频器被编程为产生1MHz 输出、则触发脉冲发生器将产生一个1MHz 周期且脉冲宽度为1/(2 * 1 MHz)的脉冲。 由于 脉冲发生器只是选通 SYSREF 分频器、因此 SYSREF 分频器需要与时钟同步以确保正确对齐。 数据表第8.3.4.1和8.3.5节提供了有关如何确保 SYSREF 分频器根据需要与器件时钟对齐的指导。