主题中讨论的其他器件:LMK5B12204、 CDCE913

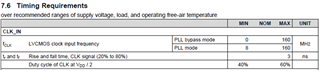

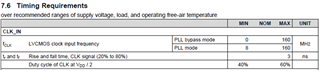

数据表 P8中介绍了时序要求的推荐规格、但未描述抖动规格。

是否有必要的抖动输入规格?

此致、

聪

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

数据表 P8中介绍了时序要求的推荐规格、但未描述抖动规格。

是否有必要的抖动输入规格?

此致、

聪

Kadeem 您好!

是否有仿真器工具可查看 CDCE813的输出时钟特性、如 TICS Pro?

这次我们的工作条件是输入时钟24.576MHz 具有来自数字 PLL 输出的4ns 抖动、然后我们期望 CDCE813具有消除抖动的功能来获得干净的24.576MHz 输出。 CDCE813输出时钟抖动的最佳仿真结果是什么?

在此条件下运行 Webench、结果随附。 LMK5B12204是成本最低的解决方案、并获得125fsrms 的输出抖动。 但它仍然有一点贵、且性能非常好。

此致、

望月市

e2e.ti.com/.../cta_2D00_export_5F00_2023_2D00_11_2D00_6_5F00_23_3B00_42_3B00_14.pdf